CVAX-based Systems

# Digital Technical Journal

Digital Equipment Corporation

Number 7 August 1988

Managing Editor Richard W. Beane

Editor Jane C. Blake

**Production Staff**

Production Editor — Helen L. Patterson Designer — Charlotte Bell Typographers — Jonathan M. Bohy Margaret Burdine Illustrator — Deborah Keeley

#### Advisory Board

Samuel H. Fuller, Chairman Robert M. Glorioso John W. McCredie Mahendra R. Patel F. Grant Saviers William D. Strecker Victor A. Vyssotsky

The *Digital Technical Journal* is published by Digital Equipment Corporation, 77 Reed Road, Hudson, Massachusetts 01749.

Changes of address should be sent to Digital Equipment Corporation, attention: List Maintenance, 10 Forbes Road, Northboro, MA 01532. Please include the address label with changes marked.

Comments on the content of any paper are welcomed. Write to the editor at Mail Stop HLO2-3/K11 at the published-by address. Comments can also be sent on the ENET to RDVAX::BLAKE or on the ARPANET to BLAKE%RDVAX.DEC@DECWRL

Copyright © 1988 Digital Equipment Corporation. Copying without fee is permitted provided that such copies are made for use in educational institutions by faculty members and are not distributed for commercial advantage. Abstracting with credit of Digital Equipment Corporation's authorship is permitted. Requests for other copies for a fee may be made to Digital Press of Digital Equipment Corporation. All rights reserved.

The information in this journal is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

ISSN 0898-901X

Documentation Number EY-6742E-DP

The following are trademarks of Digital Equipment Corporation: ALL-IN-1, DEQNA, HSC70, J-11, MicroVAX, MicroVAX II, MicroVAX 3000, NMI, NOTES, Q-bus, Q22-bus, RA81, RA82, RD54, RQDX3, RX50, TK50, ULTRIX-32, VAX, VAX-11/780, VAX-11/782, VAX 6200, VAX 6210, VAX 6220, VAX 6230, VAX 6240, VAX 8200, VAX 8300, VAX 8650, VAX 8800, VAX 8840, VAXBI, VAXELN, VAX MACRO, VAX SPM, VAX/VMS, VMS,

Compu-Share is a trademark of Compu-Share, Inc.

GDS II is a trademark of Calma Corporation.

SPICE is a trademark of the University of California at Berkeley.

Tektronix and DAS are trademarks of Tektronix, Inc. Book production was done by Digital's Educational Services Media Communications Group in Bedford, MA.

#### **Cover Design**

Systems based on Digital's advanced CMOS technology are featured in this issue. The graphic on our cover includes the lattice structure of the silicon crystal, a basic element of this technology. The expansion of the image expresses the performance growth and the system extensibility of the new CVAX-based systems.

The cover was designed by Barbara Grzeslo and Jacquie Hockaday of the Graphic Design Department.

## Contents

8 Foreword Robert M. Supnik

**CVAX-based** Systems

- 10 An Overview of the VAX 6200 Family of Systems Brian R. Allison

- 19 **The Architectural Definition Process of the VAX 6200 Family** Brian R. Allison

- 28 Interfacing a VAX Microprocessor to a High-speed Multiprocessing Bus Richard B. Gillett, Jr.

- 47 The Role of Computer-aided Engineering in the Design of the VAX 6200 System Jean H. Basmaji, Glenn P. Garvey, Masood Heydari, and Arthur L. Singer

- 57 *VMS Symmetric Multiprocessing* Rodney N. Gamache and Kathleen D. Morse

- 64 *Performance Evaluation of the VAX 6200 Systems* Bhagyam Moses and Karen T. DeGregory

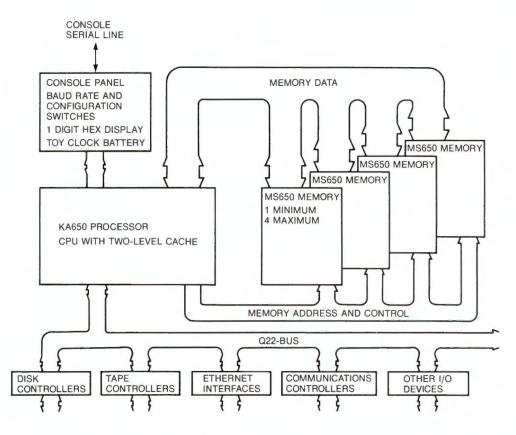

- 79 Overview of the MicroVAX 3500/3600 Processor Module Gary P. Lidington

- 87 Design of the MicroVAX 3500/3600 Second-level Cache Charles J. DeVane

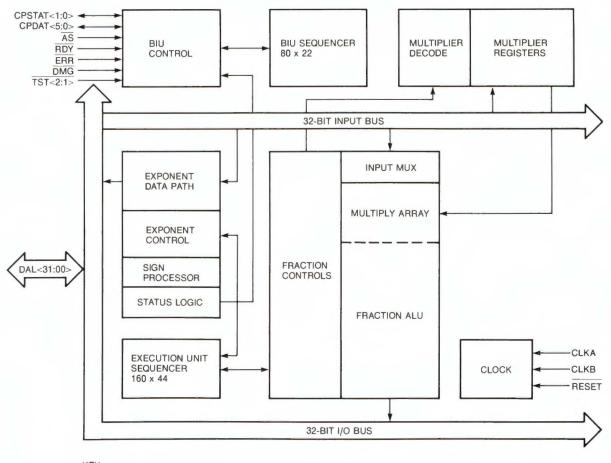

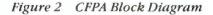

- 95 **The CVAX 78034 Chip, a 32-bit Second-generation VAX Microprocessor** Thomas F. Fox, Paul E. Gronowski, Anil K. Jain, Burton M. Leary, and Daniel G. Miner

- 109 **Development of the CVAX Floating Point Chip** Edward J. McLellan, Gilbert M. Wolrich, and Robert AJ Yodlowski

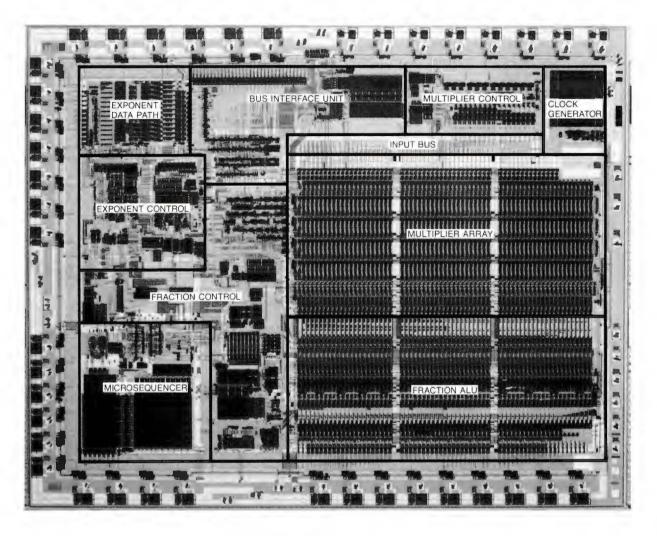

- 121 **The System Support Chip, a Multifunction Chip for CVAX Systems** Jeff Winston

- 129 Development of the CVAX Q22-bus Interface Chip Barry A. Maskas

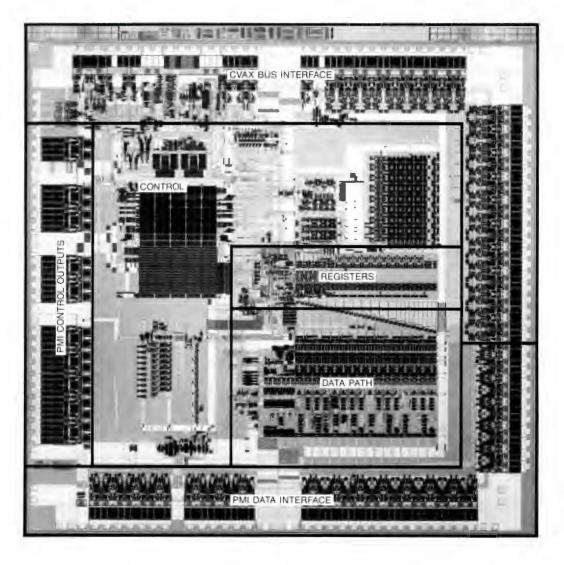

- 139 The CVAX CMCTL A CMOS Memory Controller Chip David K. Morgan

### **Editor's Introduction**

Jane C. Blake Editor

The second issue of the *Digital Technical Journal* (March 1986) featured papers on the then recently announced MicroVAX II system, a system based on a single-chip VAX implementation. In this seventh issue, we present papers on the second generation of that chip set, CVAX, the two new systems that take advantage of its increased performance capabilities, and a new version of the VAX/VMS operating system for symmetric multiprocessing.

The new mid-range system based on the CVAX chip set is the VAX 6200 family of computers, which utilizes a multiprocessing architecture. The first of two papers by Brian Allison is an overview of this highly configurable, expandable system. Brian's second paper offers insights into the architectural definition process for the 6200.

One of the major decisions made by the 6200 engineers was to design a new interconnect to support the multiprocessor system. Rick Gillett presents an informative discussion of the complexities involved in interfacing a microprocessor to a high-speed, multiprocessing bus.

To ensure the availability of first-pass functional parts, a design verification team of engineers worked in parallel with the 6200 module designers. Jean Basmaji, Glenn Garvey, Masood Heydari, and Art Singer discuss the computeraided engineering and verification principles the team instituted for the project.

Rod Gamache and Kathy Morse then describe the major features of symmetric multiprocessing in the VAX/VMS operating system. Of particular interest is their description of a new synchronization method implemented in VAX/VMS version 5.0. In the last paper related to the VAX 6200 system, Bhagyam Moses and Karen DeGregory describe the development of workloads to measure VAX 6240 performance. As part of their discussion, they include performance measurements and analysis.

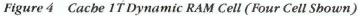

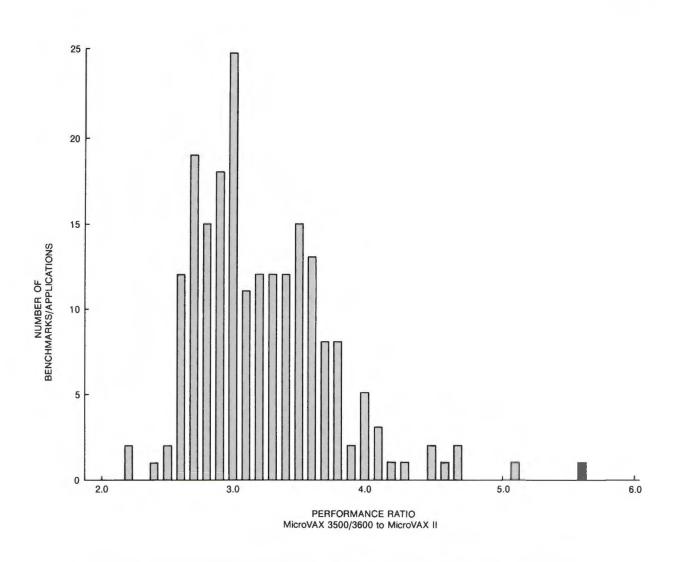

The second new system based on the CVAX chip set is the low-end MicroVAX 3500/3600 system, which offers three times the performance of its predecessor, the MicroVAX II. In his overview of the major sections of the processor module, Gary Lidington relates how schedule and performance requirements influenced product design decisions.

Charles DeVane then describes the MicroVAX 3500/3600 system's two-level cache architecture, with emphasis on the design of the second-level cache. He also presents some cache performance test results.

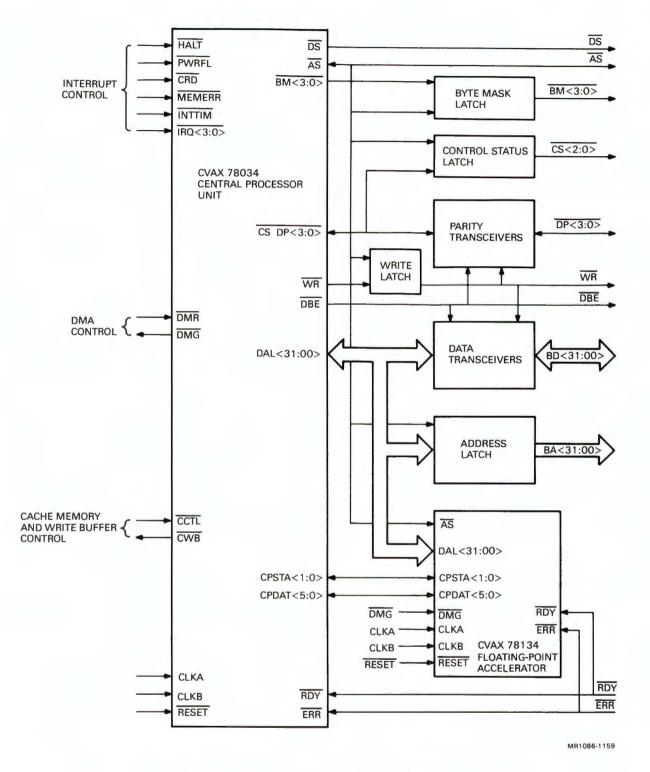

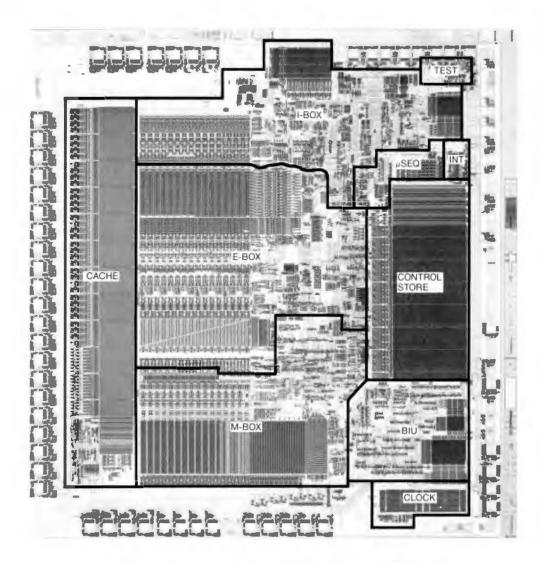

The high performance of both the VAX 6200 family and the MicroVAX 3500/3600 system is attributable in great measure to the CMOS VAX family of chips on which these systems are based. Our five final papers address the design and development of this chip set. Frank Fox, Paul Gronowski, Anil Jain, Mike Leary, and Dan Miner begin the discussion with an explanation of how designers achieved the performance goals for the single-chip VAX CPU by reducing ticks per instruction and machine cycle time.

A companion to the CVAX CPU, the floating point processor chip offers floating point performance equal to that of the microprocessor for integer operations. The approach taken to attain this goal and a description of the chip are presented by Ed McLellan, Gil Wolrich, and Bob Yodlowski.

Jeff Winston then discusses the development of the system support chip, which provides a common core of peripheral system functions.

Next, Barry Maskas relates the design efforts of three groups, one in Japan and two in the U.S., that resulted in a single-chip interface between the CVAX microprocessor and the Q22-bus I/O subsystem.

In our final paper, Dave Morgan describes the CVAX memory controller chip, CMCTL, which is optimized for Q-bus-based systems.

Jane Blake

### **Biographies**

**Brian R. Allison** Brian Allison, a consultant engineer for mid-range VAX systems, was the system architect responsible for the coordination of the VAX 6200 system definition and design. Prior to this work, he served as system architect for a project that yielded several products, including DEBNA, DEBNK, and the KA800. As a member of the VAX-11/750 design team, he wrote various portions of the microcode for that product. Brian holds a B.S.E.E. and a B.S.C.S. from Worcester Polytechnic Institute (1977).

Jean H. Basmaji Jean Basmaji is the technical director of computer-aided engineering and design-verification testing for the VAX 6200 project. A software consultant engineer, he has also been involved with CAE/DVT planning and scheduling, and has served as CAE/DVT project leader for the VAX 6200 CPU module. Jean joined Digital after receiving his B.S.E.E. from Lowell Technological Institute in 1977.

**Karen T. DeGregory** A senior software engineer in the Systems Performance Analysis Group, Karen DeGregory is project leader of systems performance measurement for the VAX 8840 and VAX 6240 systems. In addition to planning and implementing the measurements, she helped develop appropriate workloads for these systems. Prior to this work, Karen was a senior software specialist in the Software Services Backup Support Group. She received her B.S. (1980) with honors and distinction and her M.S. (1981) from Cornell University.

**Charles J. DeVane** Charles DeVane is a senior hardware engineer in the MicroVAX Systems Development Group. For the MicroVAX 3500/3600 project, he designed the second-level cache on the KA650 CPU module and guided the process of module system debug and introduction to manufacturing. Before joining Digital in 1981, Charles received a B.S.E.E. from North Carolina State University in Raleigh, North Carolina. He is a member of Eta Kappa Nu and Tau Beta Pi engineering honor societies.

**Biographies**

**Thomas F. Fox** Frank Fox, a principal engineer in the Semiconductor Engineering Group, worked on the implementation of the CVAX 78034 CPU chip. He is currently designing a high-performance microprocessor and consulting with the Advanced Semiconductor Development Group on the development of a submicron CMOS process. Frank was educated in Ireland and received a B.E. degree from University College Cork (1974) and a Ph.D. degree from Trinity College Dublin (1978), both in electrical engineering. He has published papers on ultrasonic instrumentation and magnetic resonant imaging (MRI) and has three patents pending.

**Rodney N. Gamache** A consulting software engineer in the VAX/VMS Software Development Group, Rod Gamache has been with Digital for 11 years. Shortly after receiving a B.S. in mathematics and computer science from the University of New Hampshire, he joined Digital to work on the development of DECnet Phases III and IV for both RSX-11M and VMS. For the last two years, Rod has been project leader for the VMS symmetrical multiprocessing project and has filed two patents on VMS SMP. Rod also serves as a consultant for the architectures of future low-end VAX processors.

**Glenn P. Garvey** Glenn Garvey is an engineering supervisor presently leading a team in the verification of a new VAX processor. He was the project leader for the system-level verification performed on the VAX 6200 system and has been involved in modeling and verification since coming to Digital in 1982. Glenn was a co-op student at Digital in 1980 and 1981. He holds a B.S.E.E. from Rensselaer Polytechnic Institute.

**Richard B. Gillett, Jr.** Rick Gillett, a consultant engineer, led the VAX 6200 CPU module project. Prior to his work on the 6200, he served as one of the architects of the XMI bus and was a member of the VAXBI bus project team. Relative to his work on the VAX 6200 design, he has recently filed 13 patent applications. Currently, he is system architect for a new VAX system. Rick joined Digital after receiving a B.S.E.E. (summa cum laude) from the University of New Hampshire in 1979. He is a member of Tau Beta Pi and Phi Kappa Phi.

**Paul E. Gronowski** Before receiving a B.S.E.E. from the University of Cincinnati in 1984, Paul Gronowski was a co-op student at Digital working on chips for the VAX 8200 and 8300 systems. Currently a senior engineer in the Semiconductor Engineering Group, he has been a codesigner of the E-box for the CVAX 78034 CPU chip, designer of the bus interface unit and exponent section for a CMOS floating point chip, and is now doing advanced development work for a new CMOS microprocessor. Paul is a member of Eta Kappa Nu.

**Masood Heydari** Masood Heydari is an engineering manager responsible for the computer-aided design, verification, and testing of mid-range VAX systems. He is also managing the development of an I/O subsystem for VAX products. Since joining Digital in 1981, he has developed the diagnostics for a 36-bit system and has been responsible for functional test pattern generation for several products. Most recently, he was responsible for CAD/DVT on the VAX 6200 project. Masood holds a B.S. and an M.S. in computer engineering from Boston University (1980). He is a member of Tau Beta Pi.

**Anil K. Jain** Anil Jain received an M.S.E.E. from the University of Cincinnati (1980) and a B.S.E.E. from Punjab Engineering College (1978). Upon joining Digital in 1980, he worked on bipolar and CMOS-1 technology while a member of the Device Modeling Group. As a senior engineer working on the CVAX project, Anil designed the bus interface unit for the CPU chip and has a patent pending for the bus interface protocol. He is currently working as a project leader on the floating point chip project for vector applications.

**Burton M. Leary** Mike Leary is a principal engineer in the Semiconductor Engineering Group/Advanced Development Memory Group and is currently working on the design of advanced memory products. In previous work, he participated in the design of the floating point chips for the MicroVAX and 8200/8300 systems and the design of a CMOS serial interface controller chip. Mike joined Digital after receiving a B.S.E.E. from the University of Massachusetts. He is a member of Tau Beta Phi.

**Gary P. Lidington** Currently an engineering manager in the MicroVAX Engineering Group, Gary Lidington has served as a system engineer for the MicroVAX 3500/3600 system and as a maintainability engineering project manager for the MicroVAX II and single-board computers with Q-bus multiprocessing architectures. Before coming to Digital in 1981, Gary was a co-op student and test engineer on the L200 project at Teradyne, Inc. He holds a B.S.E.E. (honors) from Tufts University and an M.S. in computer engineering from the University of Massachusetts.

**Barry A. Maskas** Barry Maskas, a consulting engineer with the Semiconductor Engineering Group, is the project leader for the development of a custom VLSI memory controller. Prior to his current work, he was the U.S. project leader and architect for the CVAX Q22-bus interface chip and codesigner of the MicroVAX IICPU and memory boards. Barry came to Digital in 1979 after receiving a B.S.E.E. from Pennsylvania State University. **Biographies**

**Edward J. McLellan** Ed McLellan is a principal engineer in the Semiconductor Engineering Group. He has worked on the design of several chips, including the J-11 and the CVAX floating point accelerator chips. He holds one patent for previous work and has made application for two additional patents based on work done for the CVAX floating point chip. Ed joined Digital in 1980 after receiving a B.S. in computer and systems engineering from Rensselaer Polytechnic Institute. Currently he is project leader for a floating point chip for a new processor.

**Daniel G. Miner** Dan Miner came to Digital after receiving a B.S. in computer engineering from Rensselaer Polytechnic Institute in 1985. A software engineer in the Semiconductor Engineering Group, he wrote the debug and diagnostic tests for the CVAX CPU chip. Dan co-authored and presented a paper on the subject of testability strategy at the 1987 IEEE International Test Conference.

**David K. Morgan** Dave Morgan is the engineering manager of Advanced Peripheral Development in the Semiconductor Engineering Group. For his work on several engineering projects, Dave has three patents pending. Before joining Digital in 1975, he was a design engineer at the RCA Solid State Division and holds five patents for his work on integrated circuit designs. Dave received a B.S.E.E. (1969) from Western New England College, an M.S.E.E. (1972) from Rutgers University, and has pursued doctoral work in solid-state physics.

**Kathleen D. Morse** As a consulting software engineer, Kathy Morse is working on advanced development for the VAX/VMS Development Group. She is one of the VMS SMP architects and consults on enhancements to various parts of the VMS executive. Earlier, she implemented the VMS support for the first MicroVAX systems, the first asymmetric multiprocessing VAX system, and the MA780 multiport memory. Kathy joined Digital in 1976 after receiving her B.S.C.S. degree from Worcester Polytechnic Institute, where she also earned her M.S.C.S. degree in 1985. Kathy is a member of IEEE, the Professional Council, and ACM as well as Tau Beta Pi and Upsilon Phi Epsilon.

**Bhagyam Moses** Bhagyam Moses is the engineering manager of the Midrange Systems Performance Analysis Group, a group which she established two and a half years ago. Prior to her current work with the VAX 8000 and VAX 6200 series of systems, she had been involved in the modeling and performance measurement of the VAX 8600 and 8650 systems, PDP-11 systems, DECSYSTEM-20, and earlier VAX systems. Bhagyam joined Digital in 1979. She received a B.S. degree (honors) in mathematics from Spicer Memorial College and an M.S. in applied mathematics from Howard University.

Arthur L. Singer Art Singer supervises the computer-aided design, simulation, and timing verification for a new I/O adapter product. His previous work includes supervision of the system simulation and timing verification of the VAX 6200 system and microdiagnostic and release support for the VAX 8600 project. Before joining Digital in 1984, Art was employed by IPL Systems as a design engineer and manager of a microdiagnostic development group. While at IPL, he received a patent for the design of an instruction unit. He is a member of Tau Beta Pi and Eta Kappa Nu.

**Jeff Winston** A member of the Semiconductor Engineering Group, Jeff Winston designed the microsequencer for the VAX 8200 CPU chip and led the design of two generations of the MicroVAX System Support Chip. He has also contributed to the development of many CAD tools used in chip design. Before joining Digital in 1980, Jeff received his B.S. (1979) and M.S. (1980) in Electrical Engineering from Cornell University. He is currently leading the development of the XMI interface chip set for a new mid-range VAXCPU.

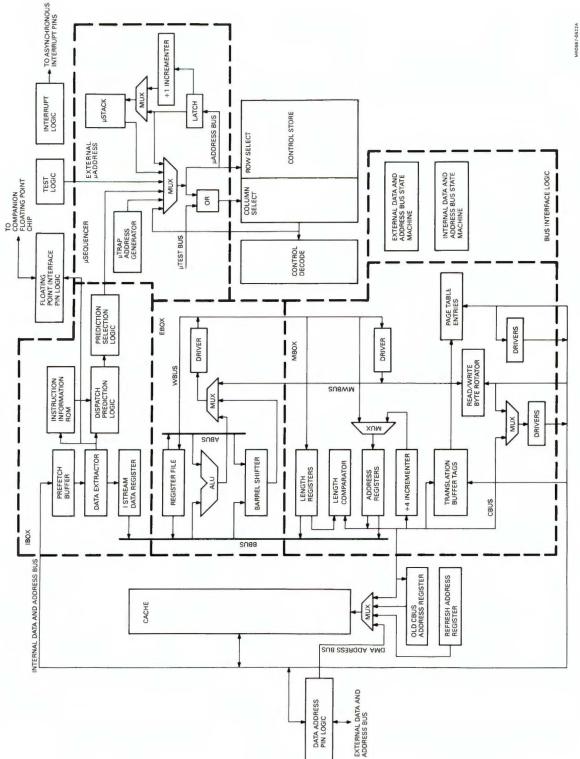

**Gilbert M. Wolrich** A consulting engineer in the Semiconductor Engineering Group/Architecturally Focused Logic, Gil participated in the J-11 control chip design and was project leader for the CVAX CFPA and the J-11 FPA chip projects. He holds a patent for an ALU with Carry Length Detection used on the J-11 FPA. Gil received a B.S.E.E from Rensselaer Polytechnic Institute in 1971 and an M.S.E.E. from Northeastern University in 1977.

**Robert AJ Yodlowski** Bob Yodlowski, a principal engineer, is the chip implementation project leader and lead circuit designer for the CVAX floating point accelerator. For his work on this project, Bob has three patents pending. He was also senior circuit designer on the J-11 floating point chip project. Relative to this project work, he is a co-inventor and patent holder for ALU with Carry Length Detection (1987). Before joining Digital in 1977, Bob was a senior member of the technical staff at LFE Corporation in Waltham, MA. He received a B.S. in engineering physics from Cornell University (1968) and an M.S.E.E. from Syracuse University (1970).

Robert M. Supnik Corporate Consultant, VLSI Technology, and Group Manager, Semiconductor Engineering Microprocessor Development

In May 1985, Digital introduced the MicroVAX II computer system. Based on the MicroVAX processor chip set, the MicroVAX II system offered unsurpassed price, performance, and reliability characteristics. In the three years since then, Digital has sold more than 100,000 systems based on the MicroVAX chip set. There are more MicroVAX-based systems in the field than all other types of VAX systems combined.

In the same three years, the practice of computer engineering has advanced considerably. Faster processors, bigger memories, quieter packages, and more complex software have appeared in a steady stream. For Digital to remain competitive, we would need, over time, a second generation of VLSI-based VAX chips and systems. The chips and systems that constitute the second VLSI-based generation are described in this issue of the Digital Technical Journal.

The planning for the second generation began in 1983. That year, the LSI Group (now Semiconductor Operations) formulated a multiyear program for the development of both semiconductor process technology and leading-edge chip products. The key characteristics of this process/ product plan were

CMOS (complementary metal-oxide-semiconductor) process technology (Previous Digital chips were based on NMOS technology.)

- Multiple process generations related by optical scaling

- VAX microprocessors as the leading edge chip development projects

- Performance improvements targeted for greater than 50 percent per year

This program not only provided the LSI Group with an overall structure for its process and chip development projects; it also provided Digital's system groups with a stable, long-term basis for planning system products.

The program was also a significant leap of faith. When it was formulated, there was no MicroVAX business. The MicroVAX II system was two years away from shipment. Almost all design resources in the LSI Group and in the low end system groups were busy with the MicroVAX chip set and its related systems. Major development projects in technology, chip design, systems design, and manufacturing were required to bring the program vision to fruition.

Work began with development of the underlying semiconductor technology. Starting in 1983, a team from Semiconductor Manufacturing's Advanced Semiconductor Development (ASD) defined, simulated, and tested CMOS-1, Digital's first CMOS process. When first defined, CMOS-1's key features — N-well base on a p-type epitaxial layer, two levels of metal interconnect, 2.0 micron feature size, direct scalability to 1.5 micron feature sizes — were controversial within an industry that was still debating NMOS versus CMOS. Over time, these choices have been vindicated, and CMOS-1 has proven to be a mainstream, robust, highly manufacturable process.

Equally important was development of design methods for larger and more complex chips. The Semiconductor Engineering Computer Aided Design (CAD) Group continuously refined the structured design process first deployed for MicroVAX and V-11. The goals of this effort were improved simulation coverage, faster turnaround time, and more extensive automated verification. One consequence of the increased use of CAD tools was a dramatic increase in the amount of computing power required. This generation of chip development projects used four times as much computing power as the first VLSI generation.

The Semiconductor Engineering Microprocessor Group began architectural prework on the second-generation chip set (called CVAX) in mid-1984. The overarching goal was simple: three times the performance of the MicroVAX chip set in less than three years — a compound performance growth rate of more than 50 percent per year. The central processor design started from the MicroVAX base but drew upon ideas from other VAX implementations, notably the 8700. The floating point unit design focused on minimal execution flows for the most common instructions. Both chips transitioned to implementation in 1985.

The original concept for the CVAX chip set had been to build chip-for-chip analogues of MicroVAX - a central processor and a floating point unit. However, as the flexibility of the new CMOS process, and the efficiency of the CAD tools, were appreciated by designers, the chip set concept expanded beyond the central processor to include key peripherals. The implementation of these peripheral functions in VLSI chips made systems faster, more reliable, and less expensive. In addition, it allowed peripheral functions to be standardized across multiple system implementations and additional functions to be added in modular fashion. The Semiconductor Engineering peripherals group (now Advanced Development) specified and implemented a memory controller, a memory driver, a console interface, and a Q-bus interface.

After the MicroVAX II system shipped in May 1985, the Low-end Systems Group and the Midrange Systems Group became actively involved in the specification of the CVAX chips and in the definition of new systems utilizing the chip set. In the low end, the 3500/3600 systems were defined as evolutionary extensions of the MicroVAX II. Nonetheless, the performance targets for the new chips posed knotty design problems for a system family bounded by both cost and packaging considerations.

In the mid-range, the system designers wished to exploit the CVAX chip set's combination of high performance and low cost by constructing an extensible multiprocessor system. They defined a new system interconnect (supported by unique chips) to provide unprecedented flexibility and extensibility in configuring systems, and new system packaging to support the concept. However, a general-purpose multiprocessor system was feasible only if the VMS operating system could take advantage of the incremental power offered by additional processors. This required a major restructuring of VMS to support symmetric (all processors equal) multiprocessing. Thus, the definition and implementation of the mid-range 6200 system family and of VMS symmetric multiprocessing support had to be closely linked.

As the engineering development projects progressed, manufacturing became heavily involved in planning and executing the transition from design to volume product. LSI Manufacturing in Hudson, Massachusetts, introduced CMOS-1 into multiple fabrication units in order to produce prototypes quickly and to ramp up to high volume production. System manufacturing groups in Westfield (Massachusetts), Albuquerque (New Mexico), Puerto Rico, and other sites worked closely with the system designers to introduce the new manufacturing processes required for system production.

The results of these development programs is a family of VAX systems with exemplary price, performance, and reliability characteristics. Moreover, the programs leave as residuals a set of VLSI components from which other products can be built, and base technology from which further advances in chip and system design will evolve. The initial program vision has been fulfilled, even exceeded. Many people, in teams and individually, worked together to bring this about. The excellence of the results reflects, in full measure, the excellence of the work that they have done.

## An Overview of the VAX 6200 Family of Systems

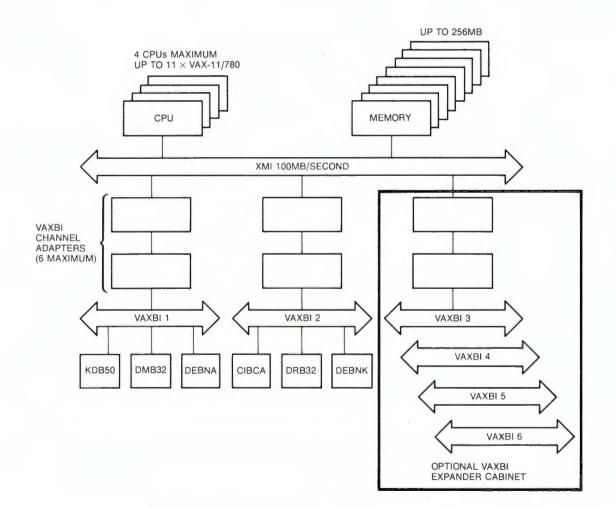

Digital's VAX 6200 series is a bigb-performance, expandable family of computer systems that combines low-cost microprocessors with bigb-performance memory and I/O subsystems. Based on the CMOS VAX chip set, the VAX 6200 CPU module performs at 2.8 times the VAX-11/780 system; utilizing a multiprocessing architecture, system speeds are available up to 11 times the VAX-11/780 system. The memory subsystem utilizes a multi-controller architecture for up to 256MB of total system memory. The XMI bus, the electrical interconnect for the system, supports the multiple processors, memory subsystems, and VAXBI channel adapters. The VAXBI is used for all I/O devices.

The VAX 6200 family of computer systems is the most recent addition to Digital's line of VAX computer systems. The VAX 6200 systems, primarily based on CMOS technology, are mid-range systems which exploit multiprocessing techniques. The VAX 6200 family currently comprises four systems, all built from common subassemblies. Any VAX 6200 system may be upgraded to any other VAX 6200 system simply by adding CPU and memory modules to the existing cabinet. This paper provides an overview of the system and therefore a context for the five papers that follow in this issue. These papers describe several of the components in detail, the engineering design effort, the performance evaluation process, and some of the multiprocessing aspects of the operating system.

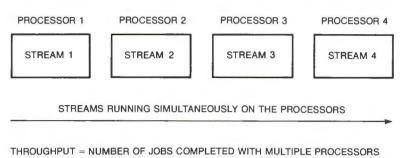

In the past, CMOS-based microprocessor technology has been used primarily to build low-cost systems. Today, by using multiples of these lowcost microprocessors, we are presented a unique opportunity to produce a high-performance computer system when the microprocessors are coupled with high-performance memory and I/O subsystems. Although this type of system architecture will not directly result in faster execution of a single task, it does result in greater system throughput in applications that have several simultaneously computable tasks. The architecture couples the effectiveness of the VMS operating system in multiprogrammed environments with hardware optimized for efficient multiprocessor operation. The result is a system that offers similar performance for a large class of applications at a better price-performance ratio than that offered by traditional single-processor, high-performance computer systems.

A primary objective of the VAX 6200 system design is to provide a highly configurable and expandable computing environment. To achieve this objective, designers chose a modular subassembly design for the total system. This modular design provides for cost-effective basic systems and also allows for system expansion to achieve higher performance. All members of the VAX 6200 family are housed in the same cabinet and use the same basic subassemblies. The only difference is the number of processors, amount of memory, and number of I/O devices. Table 1 details the configurations of the VAX 6210, VAX 6220, VAX 6230, and VAX 6240 systems.

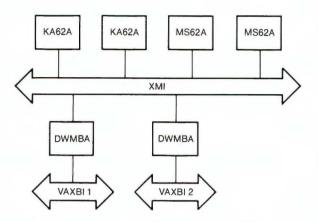

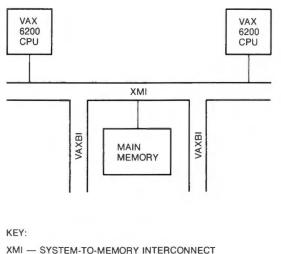

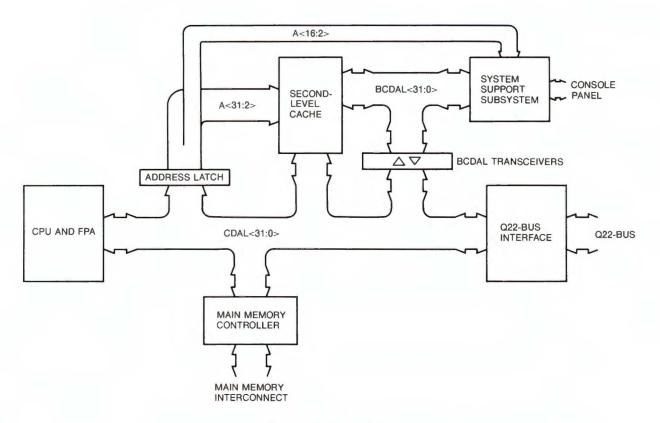

#### System Architecture

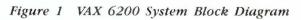

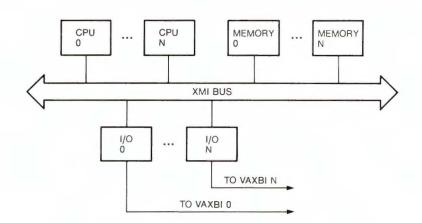

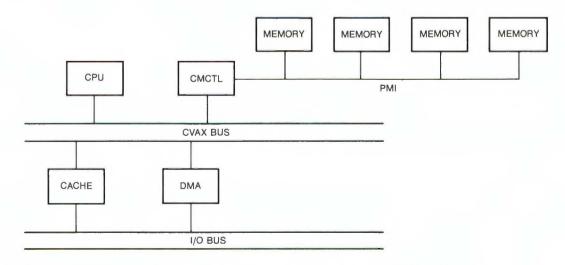

All VAX 6200 systems consist of CPU(s), memory, and I/O channel adapters connected to a common system interconnect known as the XMI. The VAXBI is used as the interconnect to all I/O devices in the system.<sup>1</sup> All memory and I/O devices are equally accessible by all CPUs in the system. Figure 1 shows a block-level diagram of the VAX 6200 system.

#### CVAX-based Systems

|                                                 | VAX 6210     | VAX 6220     | VAX 6230     | VAX 6240     |

|-------------------------------------------------|--------------|--------------|--------------|--------------|

| Number of processors                            | 1            | 2            | 3            | 4            |

| Main memory                                     | 32MB         | 64MB         | 64MB         | 128MB        |

| VAXBI channels                                  | 2            | 2            | 2            | 2            |

| CPU cycle time                                  | 80 ns        | 80 ns        | 80 ns        | 80 ns        |

| Cache size<br>(per CPU)                         | 1KB<br>256KB | 1KB<br>256KB | 1KB<br>256KB | 1KB<br>256KB |

| Free XMI slots                                  | 10           | 8            | 7            | 4            |

| Performance<br>(times one<br>VAX-11/780 system) | 2.8          | 5.5          | 8.3          | 11.0         |

| Maximum CPUs                                    | 4            | 4            | 4            | 4            |

| Maximum memory                                  | 256MB        | 256MB        | 256MB        | 256MB        |

| Maximum VAXBI                                   | 6            | 6            | 6            | 6            |

| Table 1 VAX 6200 Family System Configuration | tions | Configuration | vstem | nilv | 200 | VAX | 1 | Table |

|----------------------------------------------|-------|---------------|-------|------|-----|-----|---|-------|

|----------------------------------------------|-------|---------------|-------|------|-----|-----|---|-------|

The primary goal of the VAX 6200 system is to allow higher levels of system performance through multiprocessing. To simplify software design and to be consistent with previous multiprocessor architecture, it was essential to provide a shared memory resource. All system memory is a global resource accessible through the same address space from each processor and from all I/O devices. A sophisticated multilevel cache contained locally in each CPU minimizes memory accesses on the XMI. Cache coherency is maintained totally by hardware.

#### Technology

The VAX 6200 systems are based on a number of different CMOS technologies. The VAX CPU chip set and the system interconnect transceivers are implemented entirely in Digital's full custom CMOS process featuring a size of 1.5 microns.<sup>2</sup>

The interface between each module and the system interconnect is implemented in channelless 1.5-micron CMOS gate arrays. The number of gates used in these arrays varies from 18K to 50K gates. The interface to the VAXBI and the XMI arbitration system is implemented in 1.5-micron channeled arrays. The on-board CPU caches are implemented with 45-nanosecond (ns) 64K-by-4 CMOS static random-access memories (SRAMs) and industry-standard CMOS cache tag chips.

All VAX 6200 XMI and VAXBI modules are connected to their respective backplanes by a 300-pin zero insertion force (ZIF) connector. All modules use 10-layer controlled impedance printed circuit boards. All cables from the modules are connected through the backplane to improve reliability and to minimize the task of replacing modules.

The VAX 6200 XMI backplane is a 14-layer controlled impedance printed circuit board. Side 1 consists entirely of surface-mount contacts for the ZIF connector. Side 2 consists of plated through holes for power strips and I/O pins, and surface-mount pads for resistors. These surfacemount resistors form the termination network for the XMI signal lines.

VAX 6200 XMI modules use a printed circuit board very similar to the VAXBI printed circuit board. XMI modules have the same finger pin design as the VAXBI, but the module size is 28 cm (11.025 inches) deep instead of 20.38 cm (8.025 inches) deep.

The VAX 6200 modules make use of advanced module technology features to maximize both

the number of I/Os available to VLSI chips and the amount of logic that can be put on a module. Surface-mounted components are used extensively throughout the system. Further, many passive components and a limited number of active surface-mounted components reside on side 2 of the modules. All VAX 6200 modules limit the use of surface mount to 50-mil lead pitch components with vias on 100-mil centers. Across the modules in the system, there is a mixture of small outline integrated circuit (SOIC), plastic leaded chip carrier (PLCC), and cerquad surface-mount packages.

All VAX 6200 XMI modules interface to the XMI through a set of eight semicustom parts. These eight chips are physically mounted on a section of the module known as the "XMI corner." This section of the module is approximately 12.7 cm (5 inches) by 3 cm (1.2 inches) and is located by the A, B, and C connectors of the module. (See Figure 2.) The XMI interface area is identical on all modules so that a common electrical load is presented to all slots on the XMI. The XMI corner has four 44-pin cerquad packages on side 1 of the module and four 44-pin cerquad packages on side 2. In addition, approximately 100 surface-mounted-device (SMD) signal termination resistors and bulk power capacitors are divided evenly across both sides of the module in the XMI corner.

Figure 2 is a photograph of the three VAX 6200 XMI modules. Note that all three modules have the identical components in the lower right corner and a similar gate array directly above the XMI corner.

#### VAX 6200 CPU Module

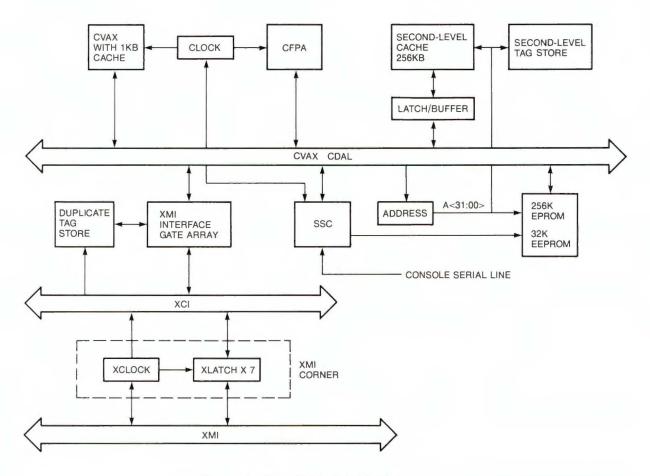

As noted earlier, the VAX 6200 CPU (KA62A) is based on the CMOS VAX chip known as the CVAX. The KA62A is a single module that implements a full CPU subsystem. Included on the KA62A module are

- The CVAX chip, which includes a 1 kilobyte (KB) on-chip cache

- An external 256KB cache

- A floating point accelerator chip (CFPA)

- Console support hardware

- An interface to the XMI

Figure 3 shows a block diagram of the KA62A module.

Figure 2 Three VAX 6200 XMI Modules

Figure 3 VAX 6200 CPU Module (KA62A) Block Diagram

Using the CVAX processor with an 80-ns cycle time, the KA62A CPU module performance is approximately 2.8 times that of the VAX-11/780 system. For a total system performance up to 11 times greater than the VAX-11/780, up to four KA62A CPU modules may be configured in a VAX 6200 system.

The KA62A CPU module contains a two-level cache to reduce memory access time. The primary cache is 1KB in size and resides inside the CVAX chip. This cache contains only instruction data to eliminate the need to invalidate this data as other processors write to cached data locations. (The VAX architecture provides strict rules for modification of instruction type data.) The secondary cache is 256KB in size and contains data as well as instructions. The KA62A monitors write transactions on the system interconnect and invalidates any cached locations written by another CPU or I/O device.

| 8-BIT<br>ECC | BANK 4 8MB (64 BITS $\times$ 1M WORDS) |

|--------------|----------------------------------------|

| 8-BIT<br>ECC | BANK 3 8MB (64 BITS $\times$ 1M WORDS) |

| 8-BIT<br>ECC | BANK 2 8MB (64 BITS $	imes$ 1M WORDS)  |

| 8-BIT<br>ECC | BANK 1 8MB (64 BITS $	imes$ 1M ,WORDS) |

Figure 4 VAX 6200 Memory Module (MS62A) Block Diagram

#### Memory

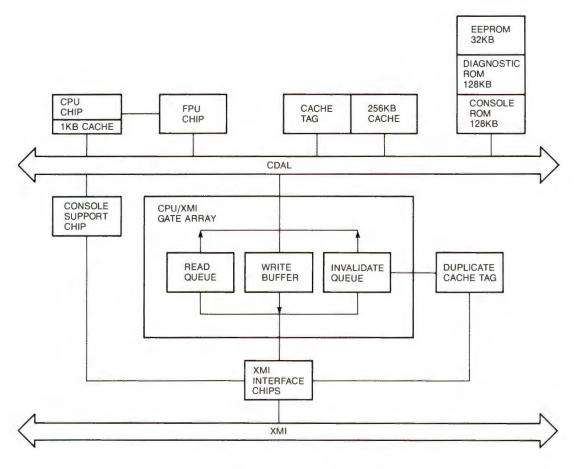

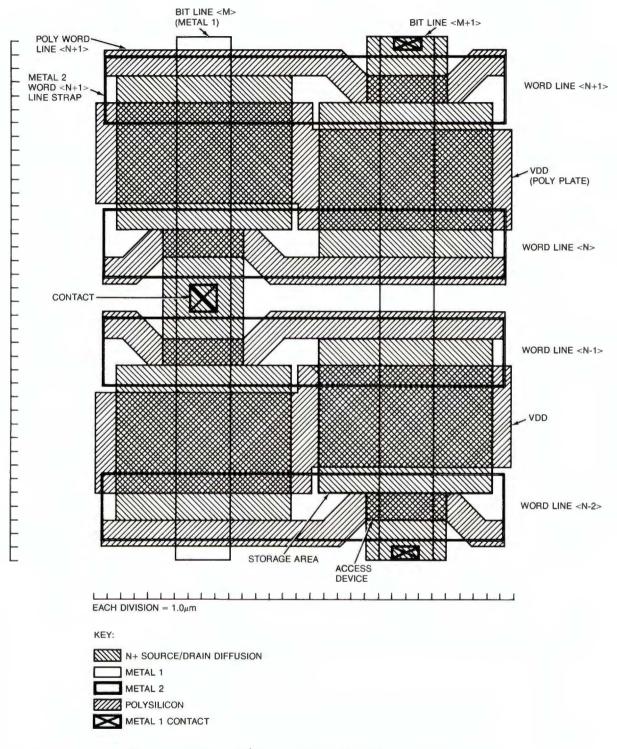

The VAX 6200 memory subsystem is made up of memory controller/array modules and is known as the MS62A. The MS62A module, shown in Figure 4, contains a memory controller chip and 32 megabytes (MB) of 1-megabit (Mb) dynamic RAMs (DRAMs). The MS62A maintains a 64-bit data path between the memory controller chip and the RAMs, and implements an 8-bit error-correcting code (ECC) for each 64-bit word. The MS62A contains hardware to implement up to 16 "lockable" memory locations per memory array. These memory locks are used extensively by processors and I/O devices to ensure singular access to data structures in a shared-memory multiprocessor system.

The greater memory bandwidth required by multiple processors and I/O channels is achieved by memory interleaving. The MS62A allows interleaving on 32-byte boundaries. As long as memory addresses are randomly distributed across the lower 6 address bits, the bandwidth of the total memory subsystem can be increased linearly with the addition of interleaved memory controllers.

The MS62A memory modules may be interleaved two, four, or eight ways. The interleave factor is automatically determined by the system upon power-up or system initialization. However, designers have given the user the ability to manually specify the interleave characteristics of the memory subsystem. Up to eight MS62A memory modules may be configured in a VAX 6200 system.

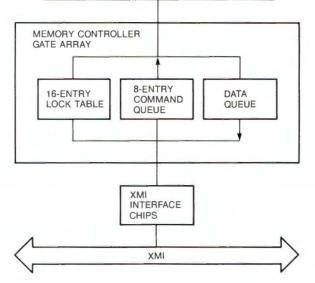

#### I/O Channels

The VAX 6200 system uses the VAXBI bus as the interconnect for all I/O devices. The system interface to the VAXBI is a two-module set called the DWMBA. Figure 5 shows a block diagram of the DWMBA modules. The DWMBA/A module is connected to the XMI, and the DWMBA/B module is connected to the VAXBI. These two modules are interconnected with a 120-wire cable assembly which may be up to 4.6 meters (15 feet) long.

The DWMBA allows VAXBI devices to read system memory at up to 5.5MB per second and to write system memory at up to 13.3MB per second. Any VAXBI-compatible device may be connected to the VAX 6200 systems through the DWMBA. All VAX 6200 systems contain a minimum of two VAXBI channels and may optionally contain up to six VAXBI channels.

#### System Interconnect, the XMI

The XMI, the primary electrical interconnect in the VAX 6200 family of computer systems, encompasses

- The protocol observed by a node on the XMI

- The electrical environment of the XMI

- The backplane

- The logic used to implement the protocol

The XMI can support multiple processors, multiple memory subsystems, and multiple I/O channel adapters.

XMI nodes may be classified as commanders or responders, depending on their role in a given transaction. A commander is a node that is initiating an XMI transaction. A responder is the node that must act upon the transaction. A processor node usually acts as a commander. (However, a processor node may become a responder if another node reads a control/status register on the CPU.) Memory nodes, on the other hand, are always responders since they cannot initiate an XMI transaction. I/O nodes may act as either commanders or responders, depending on the type of I/O operation. The functions of these nodes are further explained in sections below.

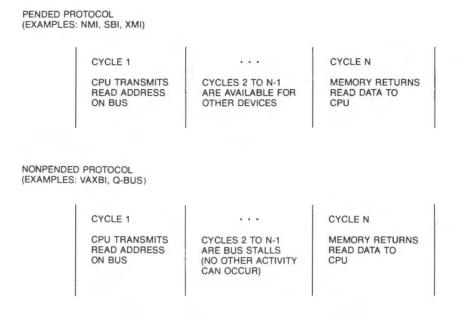

Because the XMI is a pended interconnect, several transactions can be in progress simultaneously. When an XMI commander initiates a request for a read or to solicit an interrupt vector, an identifier code is also transmitted to the selected responder. At this point, control of the XMI is relinquished, and other transactions are allowed to take place while the responder fetches the requested read data or interrupt vector. The responder then arbitrates for control of the XMI and returns the requested data or vector along with the identifier code. By monitoring the identifier codes, the initial commander is able to receive the correct data and continue.

Arbitration and data transfers occur simultaneously over a multiplexed set of address and data lines, and a separate set of arbitration lines. The XMI supports quadword, octaword, and hexword reads to memory, as well as quadword and octaword memory writes. In addition, the XMI supports longword-length read and write operations to I/O space. These longword operations implement byte and word modes required by certain I/O devices. The XMI has 30 address bits, and the smallest addressable entity is a single byte. XMI address space is divided into two halves by bit 29 of the address. When bit 29 equals zero, an address is said to fall into memory space. When bit 29 equals one, the address is said to fall within I/O space. This arrangement matches the maximum physical address as defined by the VAX architecture and allows up to 512MB of physical memory to be addressed. The XMI architecturally allows up to 16 nodes, but is physically and electrically constrained to 14 nodes.

Figure 5 VAX 6200 VAXBI Channel Adapter Block Diagram

The XMI multiplexes data and address information onto the 64-bit data path. Data transactions are initiated with a "command and address" cycle, followed by multiple data cycles. The maximum length for an XMI transaction is 32 bytes of data. The XMI cycle time is 64 ns. The effective bandwidth of the XMI is a function of the data transfer size, as shown in Table 2.

The XMI architecture allows for three distinct classes of devices.

#### **Processor Nodes**

Each processor node contains a CPU that executes instructions and manipulates data contained in XMI memory. The processor node can execute any instruction set compatible with the VAX-style byte addressing and memory locking mechanisms. A processor node will have a cache that must force all written data back to main memory. Any cached processor module must also monitor write traffic on the XMI and invalidate any location in its own cache that is written into main memory. Processor nodes must also be capable of responding to interrupt requests generated either by other processors or by I/O nodes.

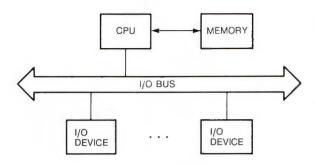

#### I/O Nodes

I/O nodes generally respond to I/O space references either by mapping the data onto another bus or by interpreting data as a command. An I/O node can also become a commander on the XMI and access global XMI memory. I/O nodes may generate interrupt sequences directed toward processor nodes. However, I/O nodes do not respond to commands directed toward memory space.

#### Memory Nodes

Memory nodes act only as responders on the XMI. They respond to read and write requests directed toward memory address space. These requests are generated either by processor or I/O nodes.

#### Data Integrity

The XMI contains a number of features to enhance the integrity and reliability of the interconnect. First, all XMI information transfer lines are parity protected, and XMI command confirmation signals are ECC protected. The XMI protocol is sufficiently robust to permit detection and recovery of all single-bit error conditions on these signals. Additionally, the XMI defines time

| Transaction Size                |                                           |  |

|---------------------------------|-------------------------------------------|--|

| Transaction<br>Size in<br>Bytes | Interconnect<br>Bandwidth<br>in MB/second |  |

| 4                               | 31.25                                     |  |

| 8                               | 62.50                                     |  |

| 16                              | 83.33                                     |  |

| 32                              | 100.00                                    |  |

#### Table 2 XMI Bandwidth Based on Transaction Size

out conditions that may be used to detect and diagnose failures.

#### VAX Console

The VAX 6200 system implements the standard VAX console functionality by means of software that conditionally executes on each of the KA62A CPU modules. Each KA62A CPU module contains a serial-line interface, 256MB of read-only memory (ROM), 32MB of electronically erasable ROM (EEROM), and 512 bytes of RAM. Control is passed to the console software upon any one of the following occurrences:

- System power-up

- Initialization

- Receipt of a control-P character from the console terminal

- Execution of the HALT instruction

- Some severe error conditions

Each KA62A CPU has access to console terminal transmit-and-receive lines carried on the system backplane. Upon power-up, control of the system console terminal is dynamically allocated to one of the CPUs present in the system. This CPU, known as the "boot" processor, provides the system interface to the console terminal as well as to the switches and lights located on the system control panel.

On receiving commands from the console terminal, the boot processor may run diagnostics or boot an operating system. This processor communicates with other processors by means of a structure maintained in memory known as the console communications area (CCA). Also considered as part of the console subsystem, a TK50 tape drive is included in each VAX 6200 system. The tape drive is connected to the system by means of a TBK50 controller module located on a VAXBI I/O channel and is used for the following purposes:

- Saving all volatile parameters for the console subsystem

- Loading the VAX Diagnostic Supervisor (VDS) when no disk is available or functional in the system

- Distributing operating system and layered software

The TK50 tape drive is also available under operating system control as a general-purpose data interchange device.

#### **Built-in Self-test**

Extensive built-in self-test is used by all modules contained within the VAX 6200 systems. Upon power-up, all modules within the system, with the exception of the DWMBA, perform a self-test in parallel. After self-test is complete, the CPU modules examine each other's status; the one in the lowest slot number that passed self-test is selected as the boot processor. The boot processor then continues to execute an additional test to ensure memory accessibility and finally executes a test of the DWMBA.

#### **Physical Packaging**

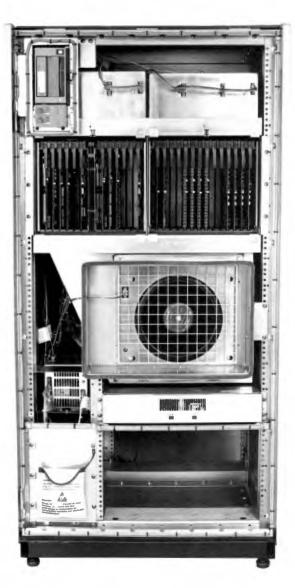

All VAX 6200 systems are housed in the same cabinet, which is 78 cm (30.5 inches) wide by 154 cm (60.5 inches) tall by 76 cm (30 inches) deep. The cabinet contains one 14-slot XMI backplane, two 6-slot VAXBI backplanes, and all necessary power and cooling to sustain a wide range of configurations. Figure 6 shows a VAX 6240 with the front door removed.

The XMI is physically implemented in a 14-slot backplane assembly containing ZIF module connectors, signal terminating networks, and a centralized clock and arbitration system. Modules are located on 2 cm (0.8 inch) centers. The XMI backplane is supplied with +5 volts (V) for general logic, a separate +5 V supply for memory,  $\pm 12$  V for the console terminal line drivers, and -5.2 V/-2 V for emitter-coupled logic (ECL). Presently none of the VAX 6200 XMI modules utilizes the ECL voltages, but ECL is included for potential future use.

Figure 6 VAX 6240 System, Front Door Removed

The VAX 6200 systems all contain two 6-slot VAXBI backplanes, which are configured as independent channels. The first slot of each VAXBI backplane is occupied by the DWMBA/B module, leaving 5 slots for standard VAXBI interfaces. All systems contain a DEBNK TK50 tape controller and a DEBNA Ethernet controller as standard equipment. The two VAXBI backplanes are supplied with +5 V,  $\pm 12 \text{ V}$ , -5.2 V, and -2 V.

#### Summary

The VAX 6200 family of systems merges the CMOS VLSI VAX chip, which is used in a number of Digital's products, with a very high perfor-

mance memory and I/O subsystem. This hardware, combined with the new fully symmetric multiprocessing capabilities of VMS version 5.0, allows very high system throughput previously achievable only with ECL technology. Moreover, the extensive use of CMOS technology results in physically smaller systems. These smaller systems consume less power and are more reliable due to the lower component count and lower power consumption.

#### References

- P. Wade, "The VAXBI Bus A Randomly Configurable Design," *Digital Technical Journal* (February 1987): 81-87.

- 2. T. Fox, P. Gronowski, A. Jain, B. Leary, and D. Miner, "The CVAX 78034 Chip, a 32-bit Second-generation VAX Microprocessor," *Digital Technical Journal* (August 1988, this issue): 95-108.

## *The Architectural Definition Process of the VAX 6200 Family*

The architectural definition of Digital's VAX 6200 family was governed by a twofold goal: to build a system with bigher throughput than previous CMOS, Q-bus-based systems at a cost lower than ECL-based systems. Decisions made during the definition process were influenced by firm schedule guidelines. Further, the very nature of the multiple processor system imposed its own requirements, particularly in the definition of the XMI bus. This new 64-bit-wide interconnect is specifically designed to meet the memory and I/O needs of the symmetric multiprocessor system. Throughout the architectural definition process, engineers continually evaluated the interdependency of one design decision upon another and against the project and schedule goals. By this process, the total definition of the system — the XMI bus, the processor module, memory module, console subsystem, and packaging — was achieved.

Definition of the VAX 6200 family of systems began in March 1985. The engineers' intent was to design a follow-on product to the VAX 8200/ 8300 family of systems, still in development at that time. This paper discusses the system architectural definition process that took place during 1985.

Like the VAX 8200/8300 family before it, the VAX 6200 family provides a system environment for a VLSI VAX chip set. This new family of systems is a mid-range VAX implementation. In this context, a mid-range system is defined as a product with more capability than the Q-bus-based systems and less capability than the emitter-coupled logic (ECL) based systems.

#### **Project Goals**

The primary goal of the VAX 6200 program was twofold: to build a system with greater system throughput than the CMOS, Q-bus-based VAX systems, and to ensure system cost was lower than that of high-performance ECL-based systems. Designers would achieve this goal by designing a system architecture that allows a moderate number of low cost CMOS VAX microprocessors to share a common system environment. Such an efficient multiprocessor system environment would offer higher throughput for a large number of applications and at a cost lower than a high-performance single processor. Once the decision to build a multiprocessor was made, the next question was how many processors to include. Several small computer manufacturers were building 8- to 32-processor systems at the time. Our belief was that the market for systems with numerous processors was fairly small because few applications would run efficiently on these systems. Therefore, we decided to design the VAX 6200 as a 4-processor system, with the possibility of expansion to 8 processors. This arrangement would allow us to still configure cost-effective 1- to 2-processor systems. If we found a significant number of applications could benefit from the larger number of processors, we could expand to 8 processors.

Building an efficient multiprocessor system would necessitate optimization of both hardware and software functionality. The VMS asymmetric multiprocessing code (VMS versions 2 through 4) that supported the VAX-11/782, VAX 8300, and VAX 8800 systems worked well for computebound, dual-processor systems. However, asymmetric operating system software would not be acceptable for larger scale multiprocessors. In the existing VMS asymmetric multiprocessing design, most operating system code was executed on the processor designated as the "primary" processor. Whenever a process needed to perform I/O or invoke most of the VMS system services, the process would have to be scheduled on the primary processor. The task of making VMS more symmetric in its handling of I/O and VMS system services was undertaken to support the VAX 8840 and the VAX 6200 families.<sup>1</sup>

Discussion of how we chose to optimize the VAX 6200 hardware begins in the section The System Interconnect.

#### Schedule

In March 1985 the design of the CVAX chips was already well under way. These chips would be delivered in time to allow systems to ship in late 1987. Based on the CVAX chip set schedule, we established the following schedule for the development of the VAX 6200 system:

Six months of architectural definition

Twelve months of design/simulation

Three months to build and test approximately five first-pass prototypes

Six months to build approximately 70 secondpass prototypes

Three months for final testing and manufacturing introduction

This two and a half year schedule significantly influenced the definition of the system architecture as well as the selection of implementation technologies. (Actual implementation took three years. The design/simulation phase took three months longer than expected, and the first-pass prototype phase took three months longer than expected.)

#### **The System Interconnect**

The first order of business was to define a new system interconnect. This interconnect would have the bandwidth required to support the memory and I/O needs of the multiple processors. We outlined three requirements that would affect the design of the new system interconnect.

- We estimated that each CVAX processor would require between 3 megabytes (MB) and 6MB per second of data to/from memory. This rate would depend on the clock rate of the processor, the selected cache architecture, and the cache "hit" rate of the program being executed.

- We also estimated that each processor could require peaks of 1MB to 1.5MB per second of I/O bandwidth.

• To maintain predictable memory access time, we decided that the system bus should not be run over 75 percent utilized.

Using the worst-case anticipated bandwidth needs, 80MB per second of peak bus bandwidth would be required to support 8 processors.

Because of the tight schedule and our awareness of the significant amount of time needed to design a new system bus, we first looked into the feasibility of using an existing bus. We considered but rejected the existing VAXBI bus, the primary interconnect for the VAX 8200/8300 system, because of its limited 13.3MB per second bandwidth. We also rejected the NMI bus, the VAX 8500/8700/8800 family interconnect, because this bus uses ECL technology. At one point we even considered using the SBI from the VAX-11/780 system with a 64-bit data path instead of its existing 32-bit data path. After extensive analysis, however, we decided a new system bus would have to be engineered for the product to meet its goals.

Although we would have to define a new bus for processor-to-memory communications, the schedule did not allow us to design a full complement of I/O interfaces for the new bus. Since a large number of I/O interfaces would be available on the VAXBI, the design team decided to use the VAXBI as the interconnect to all I/O devices. The new system interconnect, the XMI, would be used only to connect processors, memories, and VAXBI channel adapters. Therefore, in addition to the requirements listed above, the XMI architecture would also allow multiple VAXBI channel adapters to optimize I/O throughput where necessary for large systems. Use of the VAXBI for I/O adapters also had the positive effect of minimizing the number of electrical interconnects to the XMI; the physical length of the XMI would consequently be shorter and the total capacitance lower. Further discussion of the channel adapters is presented in the section VAXBI Channel Adapters.

In June 1985 a team of 11 senior-level engineers was assembled to produce the architectural and electrical specification for the XMI bus and the VAX 6200 system. In addition to architectural and electrical experts, this team included one representative from each of the anticipated module design teams. Almost all members had previously worked on projects involving the VAXBI bus. It was understood that the XMI would be used solely for the VAX 6200 family of systems, unlike the VAXBI, which would be used across many different applications. A strict adherence to this premise greatly helped the specification team to put technical trade-offs in perspective.

#### XMI Electrical Interface Definition

Since most of the VAX 6200 system is CMOS and transistor-transistor logic (TTL) based, we immediately decided the XMI could not be implemented in ECL. To maintain a TTL-level bus and to achieve the desired bandwidth, the data path clearly would have to be 64 bits wide. Further, to meet our goal of 80MB per second bandwidth, the XMI would have to transfer 64 bits of information every 80 nanoseconds (ns). (This transfer rate assumes a protocol in which address and data are multiplexed, and up to 32 bytes of data can be transferred per address cycle.)

Several electrical alternatives were considered for the XMI. A scheme using the commercially available FutureBus components was seriously considered. However, we rejected this scheme because a large number of components would be necessary to implement the 64-bit data path.

The lack of commercially available components to drive a 64-bit bus at the required speed finally led us to a decision. We would design a bit-sliced custom CMOS bus interface chip set. Each chip would transceive 11 lines, and seven chips would be used for the entire data path. Although the "sliced" bus interface would use more module real estate than a larger chip, the sliced bus design greatly simplified the chip packaging problems. Each chip would fit into a standard 44-pin cerquad package. A sliced XMI interface also allows each chip to dissipate under 0.5 watt (W), which enhances reliability and relieves the need for heat sinks on the part. Without heat sinks, the XMI interface parts can be mounted on both sides of each module. This arrangement saves 50 percent of the real estate necessary to interface to the XMI.

To simplify the design of the full custom XMI interface parts, we would keep the functional requirements for the parts as simple as possible. The XMI interface chips have little knowledge of the XMI protocol and serve only as the electrical interface. Due to the divergent needs of processor, memory, and I/O interfaces, designers already knew that each module would need a different VLSI chip for XMI interface functions. We decided, therefore, that each module VLSI chip would be required to supply the logic to implement the bus-level protocol.

As the electrical design of the XMI progressed, a bus cycle as fast as 64 ns appeared feasible. Although not entirely necessary to support the stated system performance goals, the faster XMI cycle time was strongly pursued to gain extra margin in the system design. Furthermore, this fast cycle time would allow the possibility of system upgrades to faster processors in the future. Consequently, 64 ns became the stated goal for the XMI cycle time; 80 ns was the fall back strategy if the design complexity of a 64-ns cycle time began to place the overall project schedule at risk.

Logic design across the entire system was done assuming a 64-ns cycle time. Eventually 64 ns became the actual speed of the bus as the CMOS process was characterized and the first parts were sampled and found to contain sufficient margin to support the faster cycle time.

#### XMI Protocol Definition

XMI protocol definition took place in parallel with the electrical definition of the bus. It was clear from the start that the bus would cycle several times faster than the memory subsystem. This difference in cycle times immediately led us to the decision that the XMI would run a "pended" bus protocol. A pended bus protocol allows control of the XMI to be relinquished between a "read" command and the return of the data from the memory subsystem. With multiple processors and multiple memory controllers, several read commands could be outstanding at a time.

To optimize data traffic on the XMI bus, we needed to define data transfer commands of several lengths. Since VAX instructions may write as little as 1 byte of data, a 64-bit write command was defined. (There is a mask field associated with the write command that allows single bytes to be written.) Since the VAXBI bus already had commands to transfer 16 bytes of data per address, it was essential to allow similar commands on the XMI bus to minimize the interface complexities to the VAXBI. Eventually we added a 32-byte read command to allow processors to prefetch larger amounts of data upon cache misses. A 32-byte write command was not implemented, because it would be too great a burden for the memory controller to buffer multiple 32-byte write commands.

In many cases the protocol of the XMI is similar to that of the VAXBI. In part this similarity resulted because the designers of the XMI were very familiar with the VAXBI. The similarity between protocols was also deliberately chosen because it greatly reduced the complexity of interfacing the XMI to the VAXBI for I/O purposes.

The bus arbitration scheme is one area where designers had to deviate from the method used by the VAXBI bus. The VAXBI uses the main bus data path for arbitration, which requires extra bus cycles. This approach was not feasible for the XMI pended protocol, since two arbitrations are necessary for each read transaction. Further, the VAXBI arbitration scheme also requires a great deal of duplicated logic in every module. Due to the large number of allowable XMI nodes, it was not feasible to implement an arbitration mechanism located on an XMI module. To implement arbitration on any XMI module would have required a great number of signal pins. The solution was to implement a centralized arbiter. The XMI uses a module physically attached to the rear of the backplane as a centralized arbiter as well as the source of the master clock.

The subject of data integrity on the XMI was of great concern to the designers. Initially carrying error-checking and correction (ECC) bits on the bus was considered. However, this scheme was rejected because additional encode/decode timing would have been required, and because additional bits would have to be carried on the bus. Eventually a robust protocol was implemented based on parity detection and hardware/software retries when errors are detected. All transient single-bit errors on the XMI are recoverable.

#### XMI Physical Definition

The physical definition of the XMI was a difficult task. There were a great number of interdependent trade-offs for module size, module spacing, number of backplane slots, and cabinet size.

To minimize design complexity, we had decided at a very early stage that each module within the VAX 6200 system would implement a single function. Thus the task of designing each module was simplified and the diagnosability of the system enhanced. Initially, the size of the XMI module was largely governed by the space needs of the processor. Analysis showed that a processor based on the CVAX chip set could fit on a module the same size as the existing VAXBI module 20.32 cm (8.0 inches) by 23.33 cm (9.187 inches). In addition, 32MB of memory could fit on the same size module.

System packaging was another factor to consider in selecting the module size. From the very start of the VAX 6200 program, it was not clear what type of system-level packaging was optimal. Designers knew, however, that the larger systems would primarily be placed in computer-room environments. For these applications, a standard 153.67-cm (60.5-inch) tall cabinet would be necessary. What was not clear was if office-type packaging or rack-mount-type packaging would be required. Since VAXBI formfactor pedestal and rack-mount box packages were both available, designers found it very attractive to use the same formfactor module for the XMI to ease the development of these packages if necessary. Based on the functionality fit and the desire to potentially reuse existing packaging, we decided to adopt the VAXBI module size for the XMI.

Another advantage to using the VAXBI module size was the opportunity to use the VAXBI zero insertion force (ZIF) backplane connector. Historically, developing new backplane connector technologies has proven difficult and timeconsuming. The VAXBI uses a five-segment, 60-pin-per-segment connector. Of the 300 pins, 120 pins are assigned to the VAXBI signals and 180 pins to each module for I/O use. Since the XMI has 32 more data-path bits than the VAXBI, designers chose to allot an extra 60 pins for the XMI signals. This leaves 120 pins for general module use. Designers believed the arrangement to be acceptable, since there are no I/O modules for the XMI. The only use for the I/O pins is to connect to the VAXBI card cages. The 120 available pins are more than adequate for this function.

To meet the cycle time goals for the XMI bus, the length of the XMI would have to be limited to about 0.3 meters (12 inches) and the number of loads limited to approximately 16. The XMI protocol assumed a maximum of 16 devices would interface to the XMI bus. Eventually the number of slots in an XMI backplane became 14 for two different reasons. First, 14 slots would allow a system to have 8 processors, four memory arrays, and two VAXBI channels. Second, a 14-slot XMI backplane would be very similar in size to the pair of 6-slot VAXBIs that already existed in the VAXBI pedestal and rack-mount box packages. XMI module spacing of 2.03 cm (0.8 inches) is the same as that on the VAXBI bus. We chose this spacing to allow for heat-sink components on side 1 of the module. Enough height would remain to allow non-heat-sink, surface-mounted components on side 2.

About 18 months into the program, the module designs were complete, and both the processor module and memory module were experiencing great difficulty during printed circuit board layout. Although all components could be placed within the area available, the very high pin-count gate arrays in use (223 pins) were causing considerable routing problems. To lower the schedule risk to the program, designers decided to lengthen the module by 7.62 cm (3 inches). The impact to the computerroom packaging was minimal because a 76-cm (30-inch) cabinet depth could accommodate the change. However, the change in module length made impossible the adaptation of the existing VAXBI pedestal and rack-mount packaging to the XMI. At this time the pedestal-based strategy for the MicroVAX 3500/3600 systems was clear, thus reducing the need to package the VAX 6200 family of systems for office use. Further, extremely low sales of rack-mounted VAX 8200/8300 systems led us to the decision that a rack-mount package was not immediately necessary.

#### XMI Interface Technology

The decision to implement the XMI electrical interface in simple full custom CMOS parts dictated that each module have additional logic to complete the XMI interface and to supply module-specific logic. To simplify both the design of the XMI interface parts and the CAD tools, we decided that all module-to-XMI interfaces would be implemented in the same technology. Given the aggressive design schedule, we would need a technology that was mature as well as easy to design for.

We initially focused on a family of 2-micron CMOS gate arrays available from LSI Logic and Toshiba. However, it quickly became clear that array limitation of approximately 10,000 gates would force us to place multiple chips on each module. The use of multiple chips was highly undesirable from the perspective of design resources, module real estate, and cost. A search was started to locate a suitable alternative. To get the desired logic density, several semicustom alternatives were explored but ultimately rejected because of the immaturity of their CAD tools.

Discussions with LSI Logic Corporation led us to consider their newly developed 1.5-micron "Sea of Gates" array, which offers up to 50,000 routable gates. Although this array did not give us the mature technology we were seeking, it did appear to offer the flexibility needed by all XMI designs. We ultimately chose the LSI Logic LL10000 family of gate arrays because all designs could use the same technology. Moreover, we could focus our CAD tool development on a single technology.

The 64-bit-wide XMI data path forced the pin count of a single interface chip to be 200-plus pins. The LSI Logic LL10000 array was offered in a 223-pin pin-grid-array (PGA) package which appeared suitable. Although most of the logic on each module was implemented in surfacemounted components, we did not pursue a 223-pin, surface-mount package. We wanted to avoid the manufacturing problems presented by components with 25-mil pitch leads.

#### **The Processor Module**

The VAX 6200 processor module uses the CVAX chip set to implement the VAX instruction set. Due to an uncertainty about the final CVAX chip speed, the CPU module was designed to operate over a range of 70 ns to 100 ns. The intent was to use "binned" parts in the VAX 6200 system, and to use the "nominal" parts in the MicroVAX 3500/3600 systems. (Chip manufacturing processes yield parts of different speeds; "binning" refers to the process of testing the chips over a range of speeds.) For the CVAX chip set, the nominal parts run at 90 ns, and the binned parts run at 80 ns.

A major system-wide architectural issue, which primarily affected the processor module, was whether the cache should be write-back or writethrough. Although a write-back cache could potentially reduce the number of processor writes on the XMI by 50 percent, such a cache was complicated and had never before been designed for a multiprocessor VAX system. Our final decision was based on the need to reduce overall risk to the program. Therefore, we would implement the more straightforward writethrough cache design and build the extra bandwidth into the XMI to handle the additional write traffic.

Once the decision to implement a writethrough cache was made, the major architectural issue for the processor module became the cache organization. The CVAX chip contains an internal 1-kilobyte (KB), two-way set associative cache accessible to the internal micro engine in one cycle. Due to the long latency to main memory, a second-level cache on the processor module was imperative. The size of the second-level cache was determined by the available static randomaccess memory (SRAM) technology. The newly available high-speed 64K-by-4 SRAMs would provide a 256KB cache with only eight parts. Although no accurate simulation was available to indicate the effect of this large cache, the effects were assumed to be positive. Therefore we decided that the higher cost of the SRAMs was a worthwhile trade-off given the potential gains in system performance.

A third major issue relative to the caches on the processor module was the invalidation scheme. In the past, VAX processors have managed cache invalidation, since processors and I/O devices have always shared a common memory subsystem. The issue of cache invalidation became much more important to our program because of the multiprocessor nature of the VAX 6200 system. This type of system could cause large amounts of stale data as a process migrates from processor to processor.

The 1KB cache contained within the CVAX chip caused the largest problem. If it were allowed to cache data that could become stale, every write to memory would potentially have to be invalidated within the CVAX cache. This meant choosing one of two approaches: (1) broadcasting every write in the system onto the CDAL bus of every processor, or (2) finding a way to maintain a duplicate tag store of tags within the CVAX chip and only passing writes known to reference cached data within the CVAX onto the CDAL. Another alternative was to cache only instruction-stream (I-stream) data within the internal cache. This alleviates the need to invalidate, because I-stream data is defined to be read-only by the VAX architecture. We projected this alternative could cause a 3 to 5 percent degradation in CPU performance.

Analysis of the cache-invalidate problem proved very difficult, because we did not know what percentage of data would be shared in this class of multiprocessor system. With the potential for 8 processors, it was clear that all writes could not be broadcast into each of the CVAX chips. The possibility of maintaining a duplicate external tag store proved to be very difficult to implement. Consequently, we chose the alternative to store only I-stream data within the internal CVAX cache.

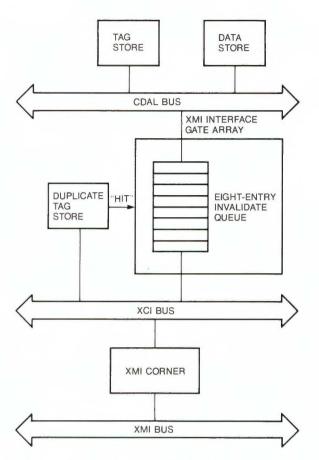

A similar problem was knowing when to invalidate data in the external cache. In this case it was feasible to implement a duplicate tag store. The second-level cache has two tag stores. One is located on the CDAL and is used for cache lookup by the CVAX chip. The second tag store is located within the XMI interface and is used to determine if XMI writes hit the second-level cache. When hits are detected, a request is queued to invalidate the entry within the secondlevel cache.

Another problem to be solved on the processor module was the issue of combining writes into larger blocks before issuing them to the XMI. Since the CDAL data path is only 32 bits wide, the CVAX chip is incapable of generating a write command any larger than 32 bits. The 64-bit data path of the XMI would need larger writes to operate efficiently. The solution to this problem was to implement a "write buffer" in the XMI interface of the processor module. The write buffer takes advantage of the fact that writes generated by VAX processors are often sequential. The write buffer will buffer up to four sequential 32-bit writes and combine them into a single XMI write transaction.<sup>2</sup>

#### **The Memory Module**

The system design goal was to provide the capacity for 15MB to 30MB of memory per processor. As mentioned earlier, the module size was partially governed by the need for 32MB of memory per memory module. The number of slots in the XMI backplane was also partially determined by the desired amount of system memory.

The wide range of possible VAX 6200 configurations dictated the need for an expandable memory subsystem. Since full memory bandwidth would only be necessary for very large configurations, it was decided to adopt a distributed memory architecture. An individual memory controller could be made simpler if it did not have to supply full XMI bandwidth. Full XMI bandwidth could be achieved by interleaving multiple memory controllers.

With the module size and number of slots determined, the first architectural decision to be

made for the memory was internal organization of the memory. The 64-bit width of the XMI made it desirable to have a 64-bit data path internal to the memory module. The very tight module real estate made it very attractive to consider implementing a 64-bit data path to reduce the number of required ECC check bits. A 64-bit-wide data path was also attractive given that the processor module would issue a read for 32 bytes whenever there was a cache miss.

The negative side of a 64-bit internal memory organization was that any write of less than 64 bits in width would result in a read-modifywrite operation to calculate the proper ECC code. An analysis of the expected write traffic through the processor's write buffer showed that approximately 50 percent of all writes would be a full 64 bits in width. Further analysis showed that as long as there was at least one memory controller for every 2 processors, there would be sufficient memory bandwidth for the system. Given the performance characteristics of the CVAX processor, it seemed reasonable to require a 32MB memory array for every 2 processors. We therefore decided to implement the 64-bit memory internal organization.

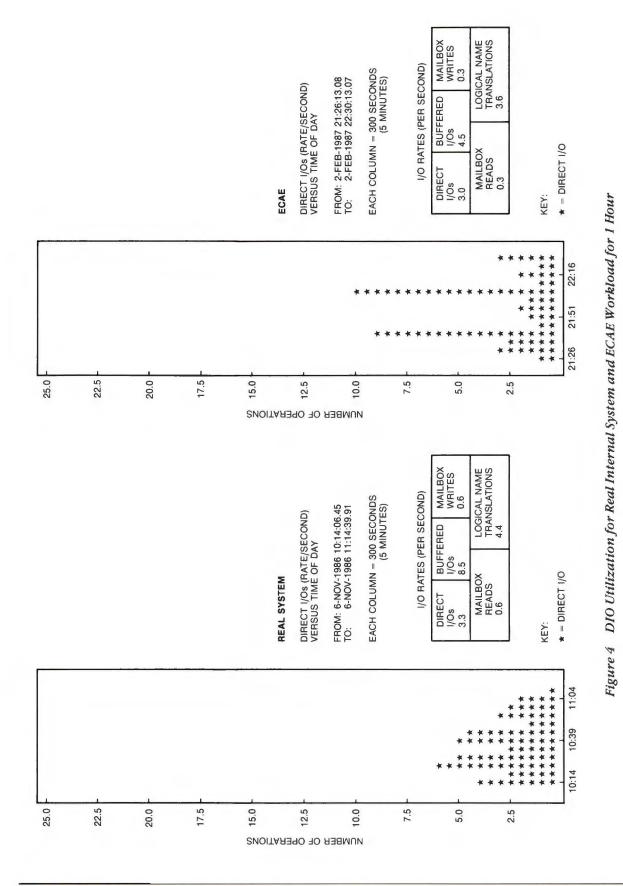

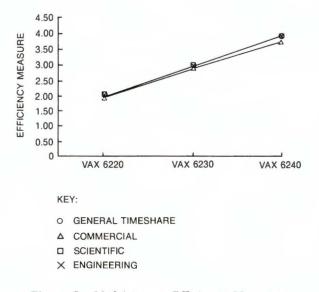

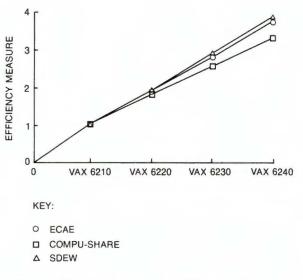

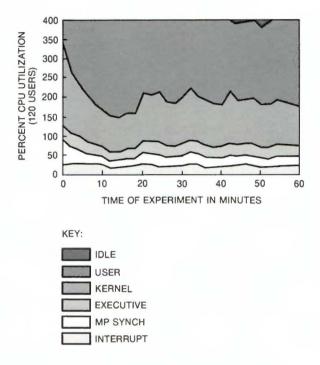

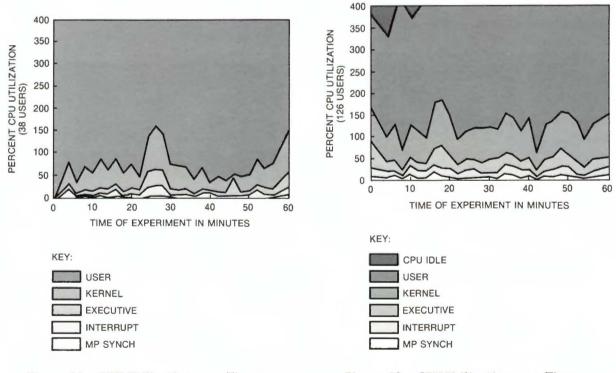

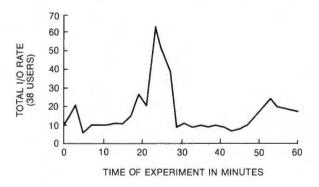

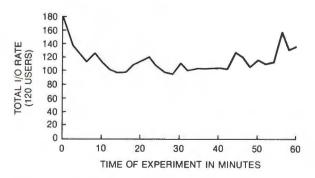

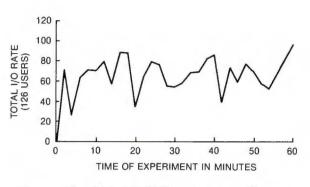

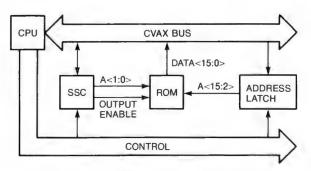

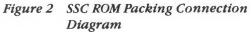

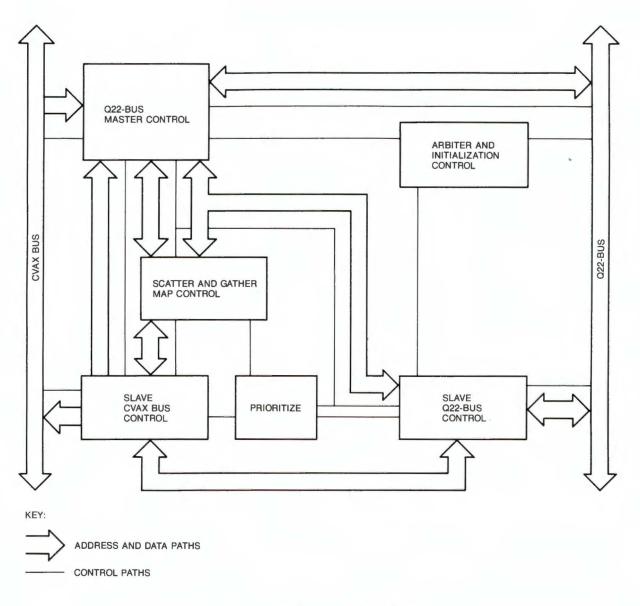

Since it was very difficult to design the memory module to accommodate the full bandwidth of the XMI, designers used memory interleaving to provide an aggregate memory bandwidth compatible with the speed of the XMI bus. The interleave size of 32 bytes was determined by the protocol of the XMI, which allows reads of 32 bytes per address cycle.