# Digital Technical Journal

Digital Equipment Corporation

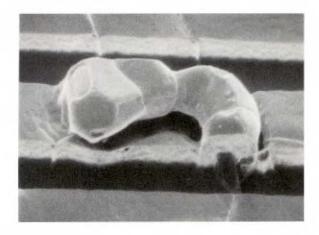

## Cover Design

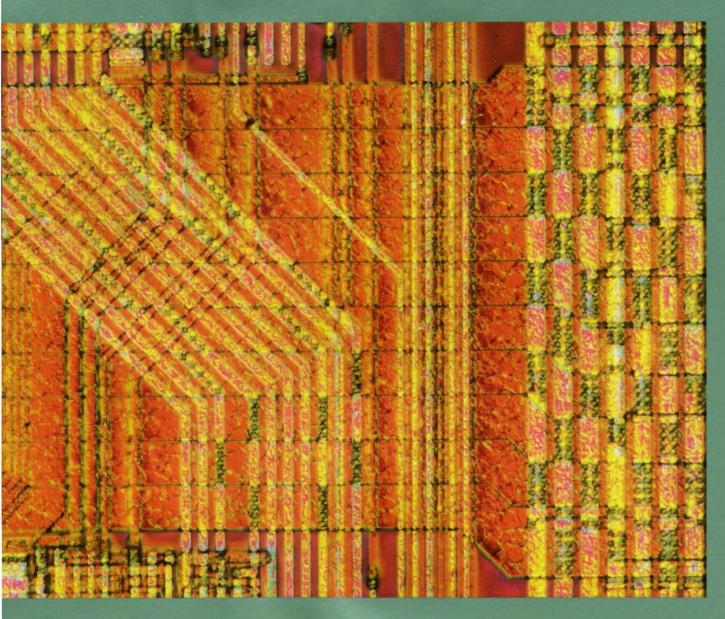

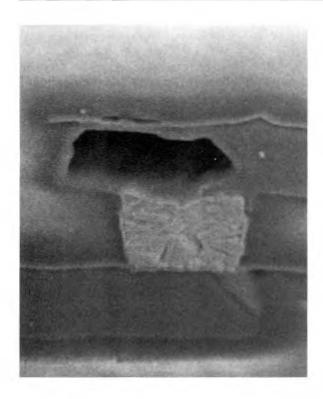

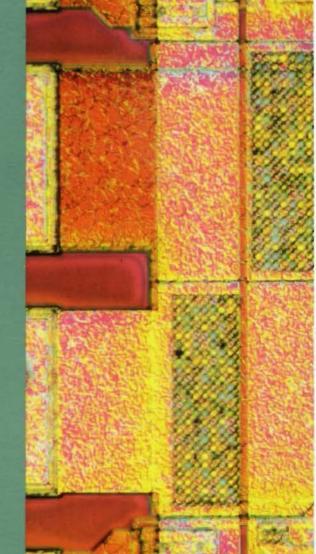

The CMOS-4 processes described in this issue are used to build Digital's high-performance NVAX and Alpha 21064 chips. The photomicrograph on our cover focuses on the high-speed clock driver and power pads of the Alpha 21064 microprocessor, which operates at a clock rate of 200 MHz.

The photomicrography is by Peter Catinella and Brian Edwards of Digital's Semiconductor Analysis Laboratory. Hudson, MA. The cover design is by Mike Call of Quantic Communications, Inc.

#### Editorial

Jane C. Blake, Editor Helen L. Patterson, Associate Editor Kathleen M. Stetson, Associate Editor

#### Circulation

Catherine M. Phillips, Administrator Sherry L. Gonzalez

#### Production

Mildred R. Rosenzweig, Production Editor Margaret L. Burdine, Typographer Peter R. Woodbury, Illustrator

#### **Advisory Board**

Samuel H. Fuller, Chairman Richard W. Beane Robert M. Glorioso Richard J. Hollingsworth Alan G. Nemeth Victor A. Vyssotsky Gayn B. Winters

The Digital Technical Journal is published quarterly by Digital Equipment Corporation, 146 Main Street MLO1-3/B68. Maynard, Massachusetts 01754-2571. Subscriptions to the Journal are \$40.00 for four issues and must be prepaid in U.S. funds. University and college professors and Ph.D. students in the electrical engineering and computer science fields receive complimentary subscriptions upon request. Orders, inquiries, and address changes should be sent to the Digital Technical Journal at the published-by address. Inquiries can also be sent electronically to DTJ&CRL.DEC.COM. Single copies and back issues are available for \$16.00 cach from Digital Press of Digital Equipment Corporation, 1 Burlington Woods Drive, Burlington, MA 01830-4597.

Digital employees may send subscription orders on the ENET to RDVAX JOURNAL or by interoffice mail to mailstop MLOT-3/B68. Orders should include badge number, site location code, and address. All employees must advise of changes of address.

Comments on the content of any paper are welcomed and may be sent to the editor at the published-by or network address.

Copyright © 1992 Digital Equipment Corporation. Copying without fee is permitted provided that such copies are made for use in educational institutions by faculty members and are not distributed for commercial advantage. Abstracting with credit of Digital Equipment Corporation's authorship is permitted. All rights reserved.

The information in the *Journal* is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in the *Journal*.

#### ISSN 0898-901X

Documentation Number EY-U5211-DP

The following are trademarks of Digital Equipment Corporation: DEC. Digital, the Digital logo, VAX, VAX 6000, VAXcluster, VAX FORTRAN, and VMS.

DEC AVS is a trademark of Stardent Computer Systems.

MIPS is a trademark of MIPS Computer Systems. Inc.

PISCES and SUPREM3 are trademarks of the Board of Trustees of Leland Stanford Junior University.

SPICE is a trademark of the University of California at Berkeley. Book production was done by the Design Group of Atlantic Graphic Services. Inc.

# **Contents**

10 *Foreword* R. J. Hollingsworth

Semiconductor Technologies

- 12 Microprocessor Performance and Process Complexity in CMOS Technologies Bjorn Zetterlund, James A. Farrell, and Thomas F. Fox

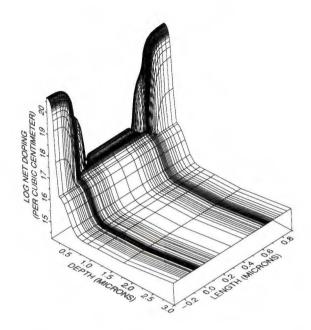

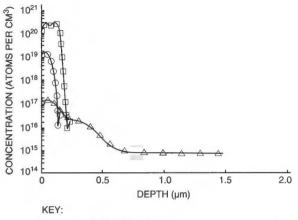

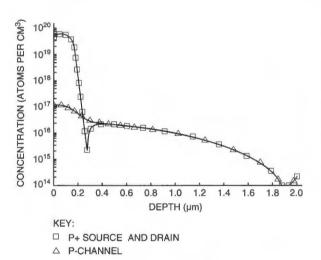

- 25 Numerical Device and Process Simulation Tools in Transistor Design Marden H. Seavey, John V. Faricelli, Nadim A. Khalil, Gerd Nanz, Llanda M. Richardson, Christian O. Schiebl, Hamid R. Soleimani, and Martin Thurner

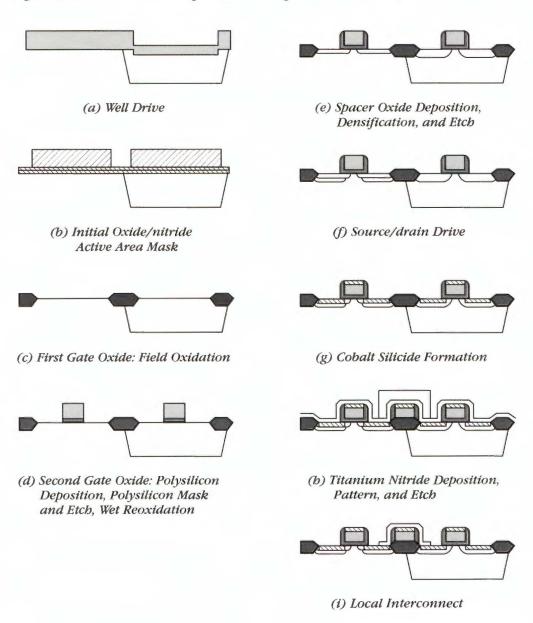

- 39 CMOS-4 Technology for Fast Logic and Dense On-chip Memory Andre I. Nasr, Gregory J. Grula, Antonio C. Berti, and Richard D. Jones

- 51 CMOS-4 Back-end Process Development for a VLSI 0.75 µm Triple-level Interconnection Technology Marion M. Garver, Joseph M. Bulger, Thomas E. Clark, Jamshed H. Dubash, Lorain M. Ross, and Daniel J. Welch

- 73 Implementation of Defect Reduction Strategies into VLSI Manufacturing

Mary Beth Nasr and Ellen J. Mager

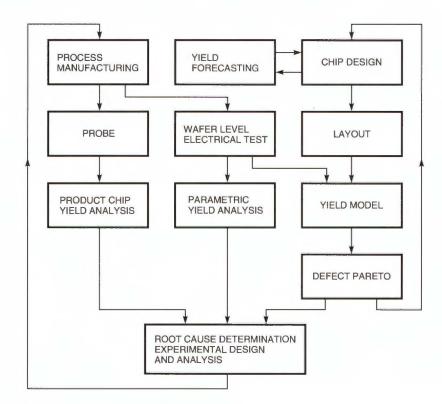

- 83 A Yield Enhancement Methodology for Custom VLSI Manufacturing Randall S. Collica, X. Joseph Dietrich, Rudolf Lambracht Jr., and David G. Lau

- 100 Transistor Hot Carrier Reliability Assurance in CMOS Technologies

Daniel B. Jackson, David A. Bell, Brian S. Doyle, Bruce J. Fishbein, and David B. Krakauer

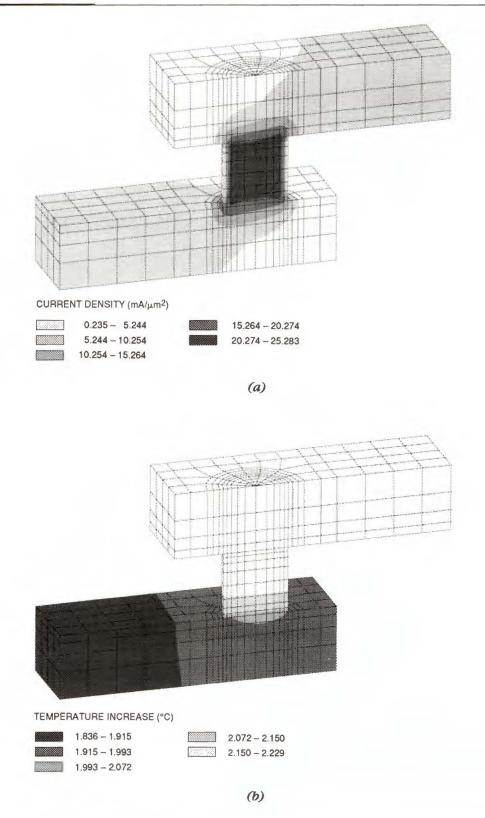

- 114 Electromigration Reliability of VLSI Interconnect

J. Joseph Clement, Eugenia M. Atakov, and James R. Lloyd

# Editor's Introduction

Jane C. Blake Editor

The design of semiconductor chips has been the topic of several past *Digital Technical Journal* issues. With the introduction of Alpha 21064, the world's fastest microprocessor, this issue focuses for the first time on the development of semiconductor technologies that make possible the high-performance of Digital's VLSI chips. Engineers in Advanced Semiconductor Development present in-depth views into CMOS-4 technologies, which produce microprocessors with up to 1.7 million transistors and operating frequencies as high as 200 MHz.

The significant increase in performance achieved with each generation of CMOS technology is in part the result of a synergistic relationship between microprocessor design and process engineers. In their paper on process technology contributions to microprocessor performance, Bjorn Zetterlund, Jim Farrell, and Frank Fox describe the scaling theory that has led to a doubling of gate density and an increase of 30 percent in gate speed in four successive CMOS generations. They discuss process features implemented in CMOS-4, and close with a discussion of models that predict process variations.

Models and tools, essential in providing designers early insight into the characteristics of the transistors to be fabricated, are the focus of a paper by Marden Seavey, John Faricelli, Nadim Khalil, Gerd Nanz, Llanda Richardson, Christian Schiebl, Hamid Soleimani, and Martin Thurner. The authors describe several physical models that accurately simulate transistor behavior, and present numerical mathematical methods used to enhance existing simulators. An overview of Digital's and others' efforts to integrate simulation tools concludes the paper.

The need for both high-density logic gates and on-chip cache memory in microprocessors presents special challenges to process engineers. Andre Nasr, Greg Grula, Antonio Berti, and Rich Jones review the front-end process (formation of device and local interconnect) for the CMOS-4 0.75- $\mu$ m technology and the steps taken to meet design requirements. They also describe the effects on submicron devices related to the scaling of feature sizes and examine some solutions.

Goals for the back-end process (formation of global metal interconnect) were also driven by the logic design requirements for higher circuit density. In addition, back-end development goals included the continued use of equipment developed for the 1.0- $\mu$ m CMOS-3 technology. Marion Garver, Joe Bulger, Tom Clark, Jamshed Dubash, Lorain Ross, and Dan Welch relate how tools were modified for CMOS-4 and describe new blanket tungsten and planarization processes for submicron devices.

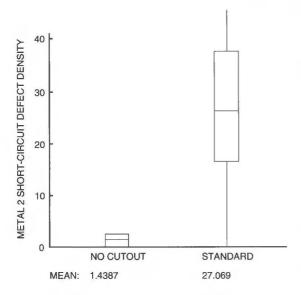

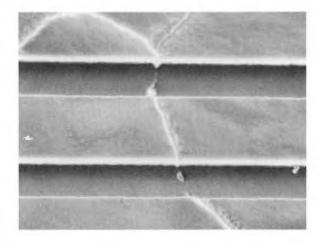

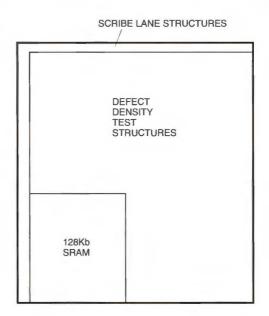

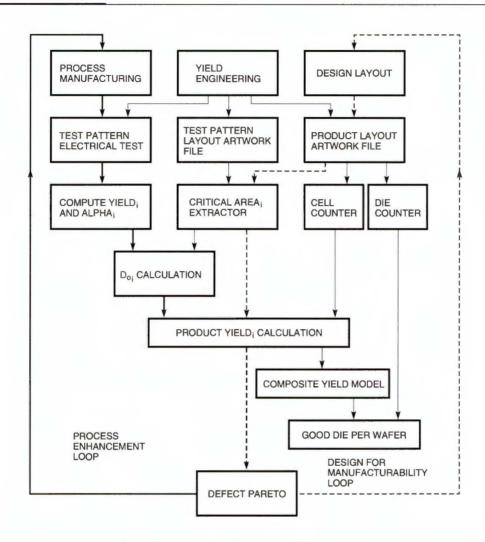

To produce a specified yield of CMOS devices, defect reduction and yield enhancements, like other processes, must be initiated concurrently with the design stage. Mary Beth Nasr and Ellen Mager review the principles of microcontamination control and outline defect reduction techniques to increase product yield in the areas of p-gate leakage and metal 2 short circuits. The paper that follows addresses the methodology of yield enhancement, including processing, process equipment, manufacturing, and design and test. Randy Collica, Joe Dietrich, Rudy Lambracht, and Dave Lau describe the use of test chip data, yield models, and the selected approach to yield analysis and forecasting.

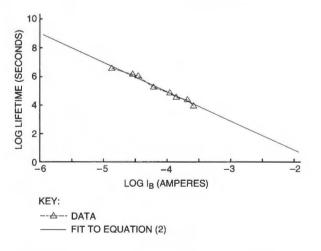

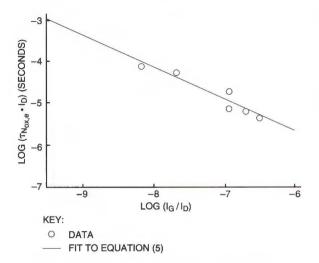

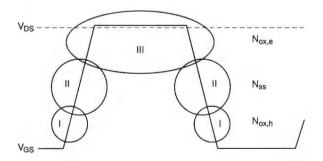

An advanced method that helps designers predict circuit hot carrier lifetime and thus maximize transistor performance at the required reliability level is the topic of a paper by Dan Jackson, David Bell, Brian Doyle, Bruce Fishbein, and David Krakauer. The authors describe a physically based method for determining the acceptability of hot carrier-induced degradation in transistor characteristics.

Another predictor of chip lifetime is the reliability of the interconnects. In their paper on electromigration reliability, Joe Clement, Eugenia Atakov, and Jim Lloyd provide a helpful overview of the potential erosion in metal interconnect due to electron conduction. They then present a scaling model developed to characterize the reliability of CMOS-4 chip interconnects.

The editors thank Rich Hollingsworth and Arlene Delvy of the Advanced Semiconductor Development Group for their guidance and unfailing support in developing this issue.

Jane Blake

**Eugenia M. Atakov** As a principal engineer in the Advanced Semiconductor Development (ASD) Group, Eugenia Atakov is responsible for evaluating on-chip interconnect reliability. Since joining Digital in 1988, she has contributed to several CMOS VLSI projects, including the Alpha 21064 chip. Previously, Eugenia worked at the Moscow Institute of Semiconductor Electronics. She received a B.S.E.E. and an M.S.E.E. from the Moscow Energy Institute, and a Ph.D. from the Moscow Institute of Steel and Alloys. She holds two patents and has published 17 papers on semiconductor device and interconnect reliability.

**David A. Bell** David Bell attended Bates College and received a B.S. degree in physics and mathematics in 1980. In 1984, he completed his Ph.D. in physics at the Massachusetts Institute of Technology. David worked at Texas Instruments on submicron CMOS and BiCMOS development prior to joining Digital's Advanced Semiconductor Development Group in 1989. His current work includes submicron CMOS transistor design, characterization, and modeling. David is a member of IEEE and Phi Beta Kappa.

**Antonio C. Berti** Antonio Berti is currently contributing to the work of the Fab 4 engineering organization as a senior engineer. He has developed and implemented CMOS-4 processes in manufacturing, including metal deposition processes for cobalt, aluminum interconnections, TiN adhesion layers, and TiN local interconnects. Antonio also developed a cobalt silicide process to decrease defects and implemented TiN deposition hardware and processes to reduce particles. He graduated from Rensselaer Polytechnic Institute in 1988 with a B.S. in materials engineering and joined Digital in 1989.

**Joseph M. Bulger** Joseph Bulger is a principal engineer with the Fab 4 manufacturing engineering organization. His main areas of involvement are thin film manufacturing, chemical vapor deposition of tungsten, and metallization. Joe joined Digital in 1988 after 10 years with Analog Devices, Inc., working on thin film development and manufacturing. He received his B.S. degree in electrical engineering from Northeastern University in 1982.

**Thomas E. Clark** A principal engineer, Tom Clark is currently a member of the CMOS-6 technology team within the Advanced Semiconductor Development Group. Tom has developed blanket tungsten plug modules for CMOS-4, CMOS-5, and CMOS-6 technologies. He also performed feasibility studies of Co and Ti salicidation processes for contact, source, drain, and gate applications in the CMOS-4 technology. Tom holds a Ph.D. in inorganic chemistry from the University of Massachusetts and has published numerous papers on the subject of CVD tungsten metallization. He has received one patent.

**J. Joseph Clement** A principal engineer on the interconnect physics project in the Advanced Semiconductor Development Group, Joe Clement works primarily on metal reliability and performance issues for VLSI. Before joining Digital in 1987, he held positions at Fairchild Semiconductor and Sandia National Laboratories. Joe received a Ph.D. in electronic materials and devices from Princeton University and a B.S.E.E. from the University of Notre Dame. He has published four papers on interconnect reliability and serves as a mentor for SRC research in electromigration at the Massachusetts Institute of Technology.

Randall S. Collica Randall Collica, a principal yield engineer, joined Digital in 1987. His primary areas of interest are SRAM fault analysis, yield modeling, fault tolerance, and experimental design and analysis. For the CMOS-4 technology, he established the use of yield models for redundancy on advanced processor chips containing on-board cache RAMs. These yield models are used for line control and productivity optimization for VLSI products. Prior to this work, Randall was engaged in failure analysis, test chip design, and process experimentation. He holds a B.S.E.E. from Northern Arizona University and is a member of IEEE.

**X. Joseph Dietrich II** Joe Dietrich is a senior engineer whose work involves yield enhancement for CMOS technologies. His responsibilities for the CMOS-4 process included work on the design for manufacturability and yield modeling. He is currently performing the same yield analyses for the CMOS-5 process. Joe has also developed photolithography processes for earlier generations of CMOS technologies. Joe joined Digital in 1983 after graduating from Rensselaer Polytechnic Institute. He was awarded a B.S. degree in physics in 1983.

**Brian S. Doyle** Born in Dublin, Ireland, Brian Doyle graduated from Trinity College, Dublin, in 1975, and received an M.Sc. and a Ph.D. from the University of London. He held a postdoctorate position at the University of London from 1980 to 1982. For the next six years, Brian was employed by Bull, France, and worked on cryogenic MOS devices and hot carrier effects. He joined Digital in 1988 and is a principal engineer in the Gate Insulator and Transistor Reliability Group. Brian is a member of IEEE and is on the technical committee for the 1992 International Electron Devices Meeting.

Jamshed H. Dubash Jamshed Dubash is a senior process engineer with the Fab 4 manufacturing organization. For the CMOS-4 technology, he developed corrosion-free metal etch processes and a sloped via process for metal step coverage. Prior to this work, he contributed to the etch process development of CMOS-3 generation semiconductors. Jamshed is currently responsible for the process development of the integration of SOG planarization processes into manufacturing. He joined Digital after receiving his B.S. degree from the Rochester Institute of Technology in 1988.

John V. Faricelli John Faricelli is a principal manufacturing engineer in the Advanced Semiconductor Development Group. Since joining Digital in 1983, he has worked on projects related to device physics and modeling, including cryogenic operation of MOS devices, hot electron effects, device isolation, and CMOS latchup. John has contributed to several device and process simulation programs, including MINIMOS, PISCES-II, and PROMIS. He holds a B.S.E.E. from Rensselaer Polytechnic Institute, and M.S.E.E. and Ph.D.E.E. degrees from Cornell University. He is a member of Tau Beta Pi and Eta Kappa Nu.

James A. Farrell Jim Farrell is a principal engineer in the Semiconductor Engineering Group (SEG). He was most recently engaged in the development of high-performance switching circuits, with particular emphasis on low-temperature operation. Prior to this work, Jim was a static RAM designer in SEG, with responsibility for developing the CMOS-3 process with the Advanced Semi-conductor Development Group and for designing several memory chips. He joined Digital in 1985, after receiving B.S.E.E. and M.E.E.E. degrees from Rensselaer Polytechnic Institute in 1984 and 1985, respectively.

**Bruce J. Fishbein** Bruce Fishbein attended Cornell University, where he received a B.S. degree in materials science and engineering in 1983. He also received M.S. (1985) and Ph.D. (1988) degrees in electrical engineering from Stanford University. Since joining the Advanced Semiconductor Development Group at Digital in 1988, Bruce has worked on gate insulator and transistor reliability for CMOS microprocessors. Specific areas of interest include time-dependent dielectric breakdown, plasma-induced dielectric damage, thermal instabilities in gate dielectrics, and the use of high dielectric constant materials.

**Thomas F. Fox** Frank Fox, a consulting engineer in the Semiconductor Engineering Group, co-led the implementation of the NVAX microprocessor and consulted with the Advanced Semiconductor Development Group on the design of the CMOS-4 technology. He joined Digital in 1984 and worked on the implementation of the CVAX microprocessor. Frank received a B.E. degree from University College Cork, National University of Ireland (1974), and a Ph.D. degree from Trinity College, Dublin University (1978), both in electrical engineering. He has published papers on ultrasonic instrumentation and VLSI design; he has two patents.

Marion M. Garver Marion Garver was the project leader and supervisor of the CMOS-4 back-end process development group and is currently performing the same function for the CMOS-6 technology. Marion joined Digital in 1980 soon after the opening of the Hudson site. She initially worked in bipolar manufacturing fabrication and joined the Advanced Semiconductor Development Group in 1982 to develop some of the original plasma etching systems for NMOS and CMOS applications. Marion holds a B.A. degree (1973) from Oberlin College and was previously employed by Alpha Industries and Ohio Medical Products.

Gregory J. Grula A consultant engineer in the Advanced Semiconductor Development Group, Greg Grula has worked on process development and integration for CMOS-1, CMOS-2, and CMOS-4 technologies. Currently he is the supervisor of the CMOS-5 front-end process technology and has performed significant work in the isolation of transistors for CMOS-5. Greg joined Digital in 1978 after five years with RCA Corporation. He received a B.S.E.E. from Wilkes University and belongs to the Electrochemical Society and IEEE. Greg was awarded one U.S. patent and has three patents pending.

Daniel B. Jackson Daniel Jackson received a B.S.E.E. (1978) from Worcester Polytechnic Institute and was awarded M.S. (1980) and Ph.D. (1985) degrees from the University of Illinois for work on semiconductor device physics. He then joined Digital, working on advanced MOS devices and process development. Daniel has managed the Gate Insulator and Transistor Reliability Group in Advanced Semiconductor Development since 1989. He is interested in advanced process development and in MOS device physics and transistor reliability. A member of IEEE, Daniel has served on the technical committee for the IEDM.

**Richard D. Jones** A principal engineer in the Advanced Semiconductor Development Group, Richard Jones developed etch processes such as local interconnect etch, polysilicon etch, and metal etch for the CMOS-4 technology. He is currently developing polysilicon etch and spacer etch processes for CMOS-6. Richard joined Digital in 1984. He received a Ph.D. (1986) and an M.S. (1982) in physics from Rensselaer Polytechnic Institute and is a member of the American Physical Society and the American Vacuum Society. He has published two papers on the properties of semiconductor materials.

Nadim A. Khalil Principal engineer Nadim Khalil is a member of Digital's Advanced Semiconductor Development Submicron Simulation Group. Currently developing optimization-based tools for process and device design, Nadim was involved in graphics and numerical software development and analytical modeling for CMOS technologies. He joined Digital in 1985, after receiving a B.S.E.E. (with distinction) from the American University of Beirut and an M.S.E.E. from Louisiana State University. Nadim is presently pursuing a Ph.D. degree at the Technical University of Vienna.

**David B. Krakauer** Since joining Digital's Advanced Semiconductor Development Group in 1989, David Krakauer has worked on topics in the area of transistor reliability, including hot carriers and electrostatic discharge (ESD). In particular, he has been involved in the design and characterization of ESD protection for Digital's advanced semiconductor processes. David graduated from the Massachusetts Institute of Technology in 1989 with S.B. and S.M. degrees in electrical engineering.

**Rudolf Lambracht Jr.** As a principal yield engineer, Rudolf Lambracht performs analysis to identify yield-limiting process steps and root causes for yield improvement. He is also interested in tools for failure analysis. Rudy worked on the CMOS-4 technology and is currently involved in the CMOS-5 technology. In his previous position as senior ion implant engineer, he was responsible for the implant process for MOS, CMOS, and advanced bipolar processes. Rudy joined Digital in 1978. He holds an A.S.E.E. degree from Waterbury State College and is coauthor of a paper concerning ion implantation.

**David G. Lau** As a senior manufacturing engineer for the Advanced Semiconductor Development Group, Dave Lau was responsible for driving yield issues during CMOS-4 development and analyzing yields for the CMOS-4 process in conjunction with the manufacturing yield group. Currently, he is developing yield strategies for CMOS-6. In a prior position, he developed and implemented device reliability characterization techniques and designed a CMOS process for liquid nitrogen temperature operation. Dave holds B.S. and M.S. degrees from MIT. He has coauthored three papers for IEEE International Electron Devices Meetings.

James R. Lloyd Principal engineer James Lloyd of the Design and Reliability Assurance Group specializes in metal reliability problems, primarily electromigration and stress voiding. He is also studying physical mechanisms related to thin film reliability in integrated circuits at the Max Planck Institut für Metallforschung in Stuttgart, Germany. Before joining Digital in 1988, Jim worked for IBM. He holds four patents, has written more than 50 papers for refereed journals, and is an invited speaker in his field. Jim received a Ph.D. (1978) from Stevens Institute of Technology in materials and metallurgical engineering.

**Ellen J. Mager** Ellen Mager is a member of the Fab 4 process engineering organization within Semiconductor Manufacturing. An engineering supervisor, Ellen is currently involved with the ongoing defect reduction of CMOS-4 material, as well as preparing for the transfer of the next technology level (CMOS-5). Ellen joined Digital in 1987 after working as a process engineer for National Semiconductor Corporation. She received her B.S. degree in chemical engineering (with high distinction) from Colorado State University.

Gerd Nanz Gerd Nanz received his Diplommathematiker degree from the Technical University of Munich, Germany, in 1985. From 1985 to 1986, he remained at the University as an assistant teacher in the Department of Civil Engineering, where he was involved in the development of self-adaptive finite element programs. Gerd then joined Professor Selberherr's group at the Technical University of Vienna, Austria, and completed his Ph.D. thesis on numerical methods in device simulation in 1989. Since 1990, he has worked on device and process simulation at Digital's Campus-based Engineering Center in Vienna.

Andre I. Nasr A consultant engineer with the Advanced Semiconductor Development Group, Andre Nasr is the project leader in the 0.35- $\mu$ m CMOS technology for front-end process development and on-chip memory implementation. He was the project leader for the CMOS-4 device group, responsible for the 0.75- $\mu$ m process and device architecture. Andre introduced and implemented the drain engineering concept in Digital's CMOS processes. He also pioneered the high-performance BiCMOS process development. Andre has one patent issued and two pending. He holds an M.S. in physics from the University of Massachusetts.

Mary Beth Nasr Mary Beth Nasr is a member of the Advanced Semiconductor Development Group. She is currently the engineering supervisor of the Metrology and Microcontamination Group, with direct responsibility for defect inspection tools. Prior to joining Digital in 1987, Mary Beth was a microcontamination control engineer for Mitsubishi Semiconductor Corporation in Japan for one and one-half years. In 1985 Mary Beth received a B.S. in chemical engineering from Columbia University and a B.S. in mathematics from Providence College.

**Llanda M. Richardson** Consultant engineer Llanda Richardson manages the Submicron Physics and Chemistry Group within the Advanced Semiconductor Development Group. She established the Device and Process Simulation Group and is responsible for ASD's participation in the Campus-based Engineering Center in Vienna, Austria. Llanda is a member of the CMOS Development Committee and Digital's alternate representative on the SRC Board of Directors. She joined Digital in 1979 after receiving a Ph.D. in physics from the University of Vermont.

**Lorain M. Ross** Lorain Ross joined Digital in 1984 after two years with NCR Corporation. She has worked primarily toward the photolithography process enhancement of several generations of bipolar and CMOS devices. Lorain participated as a member of the original task force to introduce SPC methods for controlling critical parameters of semiconductor manufacturing at the Hudson site. As a principal process engineer for the Fab 4 organization, she is responsible for the integration of newly developed photo processes into manufacturing. Lorain holds a B.S. degree in chemical engineering from Yale University.

Christian O. Schiebl Christian Schiebl received a Diplomingenieur degree in physics from the Technical University of Vienna, Austria, in 1986. The subject of his master's thesis was quantitative electron probe microanalysis (EPMA) using characteristic M-lines. He studied at the Institut für Angewandte und Technische Physik at the Technical University of Vienna and received a Ph.D. in 1989. His dissertation was on characteristic fluorescence correction in quantitative EPMA. Christian then joined the Campus-based Engineering Center in Vienna, where he currently works in the field of semiconductor process and device simulation.

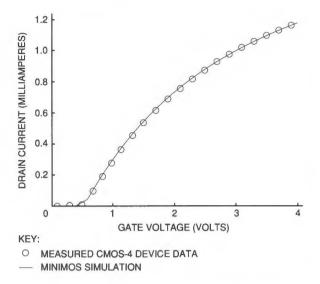

Marden H. Seavey Marden Seavey, a consultant engineer, came to Digital in 1981 from Raytheon Company. He was the supervisor of the device and process simulation projects within the Advanced Semiconductor Development Group for five years. Marden pioneered the adaptation of the MINIMOS program to the ASD CMOS process and device design. The mobility model that he developed also made it possible to apply MINIMOS in worst-case circuit design. Marden received a Ph.D. in applied solid-state physics from Harvard University. He retired from Digital in June 1992.

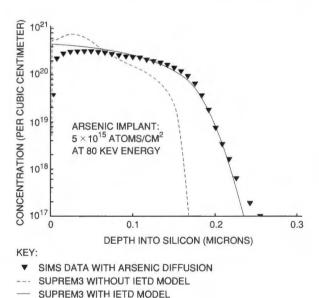

Hamid R. Soleimani Senior manufacturing engineer Hamid Soleimani joined Digital in 1987 and is a member of the Submicron Simulation Group within Digital's Advanced Semiconductor Development Group. He developed the transient diffusion model that has been incorporated in the SUPREM-III process simulation program and is used for CMOS technology development work. Hamid holds B.S.E.E. (1984) and M.S.E.E. (1986) degrees from Louisiana State University, Baton Rouge, Louisiana. He is a member of the IEEE CAD and Electron Device Societies.

Martin Thurner Martin Thurner is a principal engineer in the Submicron Physics and Chemistry Group within the Advanced Semiconductor Development Group. He is responsible for the three-dimensional device simulations investigating MOS device width effects. Martin has improved the efficiency and accuracy of the mathematical and physical models used in the MINIMOS program. Prior to joining Digital in 1988, he worked at the Federal Research and Test Institute of Austria. Martin received Diplomingenieur and Ph.D. degrees from the Technical University of Vienna, Austria.

**Daniel J. Welch** As a principal engineer in the Fab 4 process engineering thin films group, Dan Welch is responsible for the development and optimization of interlevel dielectric and planarization processes. He was project leader for the development and implementation of the SOG planarization process for CMOS-4. Dan joined Digital in 1991 after affiliation with Intel Corporation as a senior process engineer for the high-volume manufacture of advanced microprocessors. He received a B.S. in chemical engineering in 1983 from Clarkson University.

**Bjorn Zetterlund** Bjorn Zetterlund, a manufacturing consultant engineer, came to Digital in 1985 after 12 years with Raytheon Company. He is the device engineering supervisor for CMOS-5 and is responsible for CMOS-5 transistor design and the CMOS-5 technology file. Prior to this work, Bjorn was responsible for transistor design in CMOS-3 technology. He received B.S., M.E., and Ph.D. degrees in electrical engineering from Rensselaer Polytechnic Institute. Bjorn is a member of IEEE, Tau Beta Pi, and Eta Kappa Nu.

# **Foreword**

R. J. Hollingsworth Manager, Advanced Semiconductor Development

Digital has developed and manufactures the world's fastest production complex instruction set (CISC) and reduced instruction set (RISC) microprocessors. The speed of these microprocessors is due, in large part, to a complementary metal oxide semiconductor (CMOS) technology having faster transistors, as dense on-chip wiring, and innovative performance-enhancing materials and structures. This advanced CMOS technology allows Digital the unique capability to design and produce microprocessors that operate twice as fast as common leading-edge devices produced by the world's premier semiconductor manufacturers.

In 1980, Digital recognized the strategic role that microprocessor chips played as core elements in reshaping and advancing the computer industry. A key observation was that the unrelenting advances in very large-scale integrated (VLSI) circuits would continue to allow vast amounts of logic and memory to be economically produced in a single silicon chip, thereby yielding dramatic improvements in performance, cost, and reliability. VLSI devices were demonstrating yearly improvements of 10 to 15 percent in gate switching speed and 25 to 35 percent in density. Microcontamination and process control methods coupled with increasing wafer size allowed larger chips to be fabricated at lower cost. It was clear that the ability to integrate more and more function into a piece of silicon was fundamentally changing the computer industry. The era of entire computing systems on a single chip was rapidly approaching. Chips were not just components in a system, they were becoming the system. To fully exploit this and lead Digital into what C. Gordon Bell termed a "semi-computer" company in the 1990s, the decision was made to develop

and subsequently manufacture semiconductor technologies.

Digital's semiconductor operations group set a goal in the early 1980s to achieve leadership in the development and manufacture of the world's highest performance microprocessors. To meet this, a number of strategic positions were taken:

- Develop distinct generations of CMOS that would produce a wide range of VLSI devices, not only microprocessors.

- Be at the leading edge in density; be ahead of the industry in high-speed switching devices and system-level features.

- Make CMOS technology decisions by optimizing a wide range of requirements necessary to meet the goal: the world's fastest microprocessors. The approach would be a rigorous engineering optimization from computer architecture through chip manufacturing processes.

- Develop CMOS with a single, multi-disciplined technical team dedicated to the project from initial conception through manufacturing qualification—a four- to five-year endeavor.

- Use the microprocessor product, targeted to world-leading performance, as the specific focal point for CMOS development. Tie together the efforts of full-time chip architecture, design, test, reliability, packaging, and manufacturing people for the full project duration, i.e., four to five years.

- Develop CMOS technology in conjunction with the microprocessor architecture and design an essential ingredient in delivering leading VLSI chips to the market first. This "concurrent" approach has been a mainstay in Digital's CMOS development since the early 1980s.

- Participate in, contribute to, and draw upon the best semiconductor research in the world.

Many leading semiconductor companies follow these strategies. Digital, however, is unique in practicing all of them.

To help guide the technical direction, a CMOS technology roadmap was created in the early 1980s. It defined the key pacing elements that delineate each distinct CMOS generation: minimum feature size, switching speed, manufacturable chip and wafer size, and other attributes necessary to deliver leading-edge microprocessors. This roadmap set the goals for the organization and allowed easy

reference to competitive trends. In its simplest form, the roadmap defined each CMOS generation by making logic gates switch 30 percent faster while occupying half the silicon area and by integrating these elements on chips that were growing 40 percent in area compared with the previous generation. The roadmap today defines eight generations of CMOS; four have been introduced to manufacturing (CMOS-1 through CMOS-4), and two are now under development (CMOS-5 and CMOS-6).

The papers in this issue of the *Digital Technical Journal* are focused on Digital's fourth-generation CMOS (CMOS-4) that is used to build a wide variety of VLSI chips, most notably the NVAX and Alpha 21064 microprocessors. CMOS-4, presently being manufactured in Digital's semiconductor facilities in Hudson, MA, and South Queensferry, Scotland, delivers microprocessors with up to 1.7 million

transistors operating at clock rates up to 200 MHz. A variety of materials and structures have been crafted into CMOS-4, allowing advanced system-level capabilities not available in other state-of-the-art CMOS processes.

This issue spans the breadth of technical areas necessary to make CMOS-4 a successful element in establishing Digital's preeminent position in microprocessor technology. The discussions herein include how manufacturing process and chip design trade-offs are made; how a large number of complex manufacturing steps are integrated; how leading-edge speed, density, and materials are achieved; and what modeling, simulation, and measurements are critical to ensure reliability and produceability. The papers are a sample of the range of technological achievements in Digital's semiconductor operations.

# Microprocessor Performance and Process Complexity in CMOS Technologies

Digital's CMOS technology is characterized by a scaling methodology that doubles the gate density and improves the gate speed by approximately 30 percent with each new generation. Decreasing feature size from one generation of CMOS technology to the next is fundamental to improving the performance of VLSI chips. Each of Digital's successive CMOS generations has added new technology features to improve performance further. Digital's latest, qualified CMOS technology incorporates features such as low voltage operation, low-resistance topside substrate contacts, low-resistance transistor gate material, local interconnects in SRAMs, three levels of metal interconnect, and fuses for redundancy.

The goal of Digital's semiconductor organization is to provide leadership in product performance and functionality, as most recently evidenced by the Alpha 21064 and NVAX microprocessors. <sup>1,2</sup> Internal development of complementary metal-oxide semiconductor (CMOS) processes has been crucial to the success of these chips because it allowed us to design the process to meet very specific needs. The identification and fulfillment of these needs has been a multigenerational, ongoing task that closely links the chip design effort with the process development.

Each new generation of CMOS technology is scaled to double the gate density and improve the gate speed by 30 percent. In addition to the generation-to-generation improvements that are derived from scaling, a CMOS process that is designed specifically for high-performance microprocessor applications requires a number of features beyond those normally implemented in CMOS processes. As a new process is being developed, proposed new features are critically evaluated in order to arrive at the optimum trade-off between chip performance and process complexity.

This paper describes Digital's CMOS processes from the perspective of those process features that contribute to the performance and functionality of high-speed microprocessors. It begins with a short discussion on microprocessor architecture, which strongly influences the direction of process development.

# CMOS Microprocessors— General Considerations

Several factors determine the performance of the fastest microprocessor that can be built in a given CMOS technology. The performance of a microprocessor is inversely proportional to the product of clock cycles per instruction (CPI)<sup>3</sup> and the machine cycle time. From one generation of microprocessors to the next, improvements in both CPI and machine cycle time are required in order to meet the performance goal. CPI depends on the microarchitecture as well as the mix of instructions executed. The minimum machine cycle time depends only on circuit and microarchitectural issues.

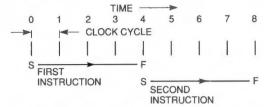

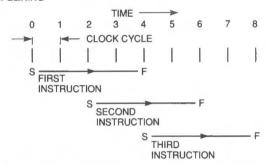

Improvements in CPI are achieved in part by pipelining and in part by adding cache memory to the die. As shown in Figure 1, pipelining is defined as the simultaneous execution of two or more instructions; for example, the first part of a two-part instruction is executed at the same time as the second part of the previous instruction. Simultaneous execution reduces the number of CPI; the result is higher performance at the expense of more circuitry. Adding on-chip cache memory also reduces the CPI. The microprocessor can quickly access instructions or data resident in its caches, rather than wait for this information to be transmitted from on-board random-access memory (RAM) chips.

#### NO PIPELINING

NO PIPELINING: Second instruction does not start until the first instruction finishes. One instruction is executed every four cycles, so CPI = 4.

#### **PIPELINING**

PIPELINING: Second instruction starts halfway through the execution of the first instruction. Third instruction starts halfway through the execution of the second. One instruction is executed every two cycles, so CPI = 2.

Note: It takes more circuitry to implement a pipeline since instructions are executed simultaneously.

KEY:

S START

F FINISH

Figure 1 Relationship between CPI and Pipelining

As the minimum feature size decreases, transistor density increases. Thus, for a given die size, a 0.75-micrometer ( $\mu$ m) minimum feature size technology (CMOS-4) can support four times as many transistors as a 1.5- $\mu$ m technology (CMOS-2). In addition, advances in process technology lead to increases in the size of the largest die that can be built with an acceptable manufacturing yield.

Microprocessor designers take advantage of the extra transistors to increase the degree of pipelining and the size of caches. This reduces the CPI, which boosts the performance of the machine. Table 1 shows the difference between two generations of scaled CMOS processes. The halving of the feature size has been augmented by a larger die size and microarchitectural changes that increase the SPECmark<sup>5</sup> performance by a factor of 4.8.

# Generation-to-Generation Scaling

The pace of improvement in microprocessor performance indicated by the REX520/NVAX comparison is ahead of the industry.<sup>6</sup> Microprocessor performance has been doubling approximately every two years, and there is no evidence that this pace of change is slackening. The shrinking of feature sizes with each new generation of CMOS process technology and the increase in yieldable die sizes have enabled this rapid improvement in the performance of very large-scale integration (VLSI) chips.

At the center of the reduction in the feature sizes of CMOS processes is the miniaturization of the MOS transistor. Over the past 15 years, a set of rules, known as scaling theory, has been developed to guide this process.<sup>78,9</sup>

In the fundamental form of scaling, called constant field scaling, the transistor's physical parameters and the power supply voltage are kept proportional to the feature sizes to maintain the magnitude and the contours of the electric fields within the transistor. All the dimensions of the transistor, e.g., length, width, gate dielectric thickness, and source/drain junction depths, and the power supply and threshold voltages are reduced by the scaling factor,  $[1/\kappa$  (where  $\kappa$  is greater than 1)], while the doping concentrations are increased by  $\kappa$ . These rules are also extended, with some exceptions, to guide the miniaturization of the interconnect. In practice, scaling theory is not followed exactly, for reasons of both performance and standardization that are discussed below. Digital's implementation of scaling through four CMOS generations is shown in Table 2.

# Improved Performance through Scaling

The reduced feature sizes made possible by scaling have a major impact on node capacitance and, hence, the speed of the chip. The minimum cycle time of a microprocessor is inversely proportional to the capacitances of the gates, sources, drains, and interconnect. The gate capacitance is inversely proportional to the thickness of the gate dielectric, and transistors with thinner gate dielectrics have higher drive current. Since the minimum cycle time is a stronger function of transistor drive current than gate dielectric capacitance, the trade-off should be made in favor of a thinner gate dielectric.

In Digital's family of CMOS processes, gate capacitances have scaled with minimum feature size.

Table 1 Comparison of Single Chip VAX Microprocessors

| Process | Minimum<br>Feature<br>Size | Chip   | Tape<br>Out<br>Date | Performance<br>SPECmarks* | Cycles per<br>Instruction <sup>†</sup> | Cycle<br>Time<br>(Nano-<br>seconds) | Chip<br>Size<br>(Mils) | No. of<br>Transistors |

|---------|----------------------------|--------|---------------------|---------------------------|----------------------------------------|-------------------------------------|------------------------|-----------------------|

| CMOS-2  | 1.5 μm                     | REX520 | Sep 87              | 8.5                       | 11.95                                  | 28                                  | 460×460                | 320,000               |

| CMOS-4  | 0.75 $\mu$ m               | NVAX   | Nov 90              | 40.5                      | 5.85                                   | 12                                  | 636×574                | 1,300,000             |

#### Notes:

Table 2 Comparison of Feature Sizes in CMOS Generations

|                                                     | CMOS-1     | CMOS-2           | CMOS-3       | CMOS-4                |

|-----------------------------------------------------|------------|------------------|--------------|-----------------------|

| Gate Dielectric Thickness (Å)                       | 300        | 225              | 150          | 105                   |

| Minimum Feature/Space (μm) Active area              | 4/2        | 3/1.5            | 2/1          | 1.5/0.75              |

| Polysilicon/polycide<br>Metal 1 with contact or via | 2/2<br>4/2 | 1.5/1.5<br>3/1.5 | 1/1<br>2/1   | 0.75/0.75<br>1.5/0.75 |

| Metal 2 with via<br>Metal 3 with via                | 5/2        | 3.75/1.5         | 2.5/1<br>4/6 | 1.875/0.75<br>3/4.5   |

| Minimum Feature Size (μm) Metal 1 contact           | 2          | 1.5              | 1            | 0.75                  |

| Metal 2 contact<br>Metal 3 contact                  | 2          | 1.5              | 1 4          | 0.75<br>3             |

| Minimum Spacing (μm) Metal 1 contact/polysilicon    |            |                  |              |                       |

| (in active area) P+/N+ active area                  | 2<br>8     | 1.5<br>6         | 1 4          | 0.75<br>3             |

From the 1.5- $\mu$ m minimum feature size of CMOS-2 technology to the 0.75- $\mu$ m size of CMOS-4, the area of the gates was scaled by a factor of four and the gate dielectric thickness was halved. The result is a twofold reduction in gate capacitance ( $C = \epsilon_0 A/t$ ). The typical gate dielectric thickness in the 0.75- $\mu$ m CMOS-4 process is 105 angstroms (Å). Manufacturability and reliability considerations have been the major factors determining the minimum gate dielectric thickness used for each generation.

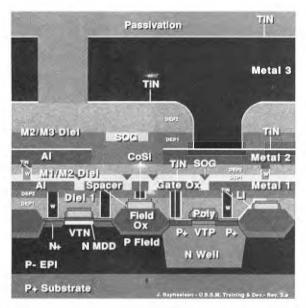

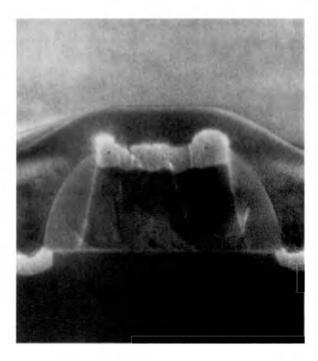

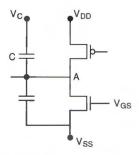

As shown in Figure 2, the sources and drains of n-channel metal-oxide semiconductor (NMOS) transistors form N+/P diodes to the substrate. Since the p-type doped substrate is held at a potential of  $V_{ss}$  (ground) and (during normal operation) the sources and drains are always at  $V_{ss}$  or higher, these diodes are always reverse biased and act as voltage-dependent capacitors. The sources and drains of p-channel metal-oxide semiconductor (PMOS) transitions.

sistors form P+/N diodes to the n-wells; the n-well is held at  $V_{dd}$  (power supply voltage).

The capacitance of a reverse-biased diode is a function of its shape and size: there is both an area component and a perimeter component.

$$C_{\text{total}} = C_{\text{area}} \times \text{Area} + C_{\text{perimeter}} \times \text{Length\_of\_Perimeter}$$

Since the area scales with the square of the minimum feature size and the perimeter scales directly with the feature size,  $C_{\rm total}$  scales by somewhat more than the minimum feature size: the exact amount depends on the shape of the source or drain. For the NVAX microprocessor, which was designed in CMOS-4, the area and perimeter components contribute about equally to  $C_{\rm total}$ . In future technology generations, the perimeter component will tend to dominate.

In Digital's CMOS processes, metal interconnect widths and spaces are scaled with the minimum fea-

<sup>\*</sup>These are combined integer and floating point SPECmarks run on a VAX 6000 Model 410 (REX520) and a VAX 6000 Model 610 (NVAX).

<sup>&</sup>lt;sup>†</sup>CPI depends not only on the CPU chip, but also on the memory subsystem and the particular program being executed. The CPI values quoted here are a composite for the ten benchmark programs in the SPECmarks suite.

ture size, but metal thicknesses and dielectric thicknesses are held constant to avoid three undesirable

Figure 2 Diagram of NMOS and PMOS Transistors Showing Gate, Source, and Drain for CMOS-4

effects. Scaling the metal thickness would increase the sheet resistance (leading to larger power supply voltage drops and RC time constant delays) and decrease the current-carrying capability of the conductor lines (from an electromigration viewpoint). Scaling the interconnect dielectric thickness would increase the capacitance per unit area. Because the thicknesses of conductor lines and dielectric layers are not scaled, the aspect ratios of the spaces between the conductors and the contacts or vias between interconnect layers increase. This makes fabrication more difficult.

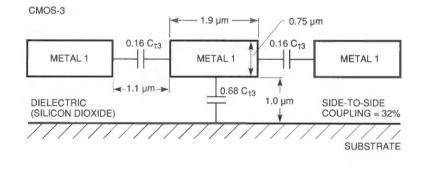

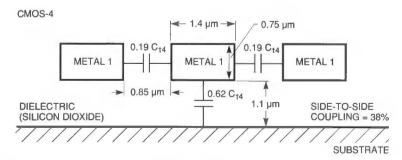

As with sources and drains, interconnect capacitance has both an area component, which scales quadratically, and a perimeter component, which scales linearly. Consequently, the total capacitance of interconnect scales by somewhat more than the minimum feature size. Because neither the interconnect thickness nor the dielectric thickness is scaled, the capacitance between adjacent conductor lines increases. The result is an increased susceptibility to cross-talk between adjacent bus signals, which is shown in Figure 3. In the NVAX microprocessor, greater-than-minimum spaces were used on some critical buses to reduce cross-talk.

Note:  $C_{13}$  and  $C_{14}$  are the total capacitances for the center line for CMOS-3 and CMOS-4, respectively. Dimensions are typical.

Figure 3 Cross Section of Three Minimum-spaced Metal 1 Lines Drawn to Scale for CMOS-3 and CMOS-4

The use of industry-standard power supply voltages results in a significant violation of constant field scaling rules. Nevertheless, power supply voltage is generally held constant across two or more process generations [5.0 volts (V) in CMOS-1 and CMOS-2 and 3.3 V in CMOS-3 and CMOS-4] in order to maintain voltage compatibility with industry-standard chips such as RAMs. However, a nonscaled power supply voltage presents formidable challenges for the design of reliable transistors.

# **Developing CMOS for Microprocessors**

The particular implementation of transistors, interconnect, and special circuit elements in a CMOS process depends on the application. For Digital's high-speed microprocessors, performance, as measured in SPECmarks, is crucial.5 In addition to optimizing the transistors for maximum drive current, performance in this application can be improved by adding process features to provide denser on-chip cache static RAM (SRAM), interconnect with high current capability, and precision resistors for impedance matching. As discussed above, performance can also be improved by increasing the die size. By contrast, a major part of the effort in designing a process for dynamic RAMs (DRAM) is directed toward developing a very small, highcapacitance memory element.

In addition to performance, the planned production volume is an important factor in defin-

ing a CMOS process. A process for low-to moderate-volume, high-performance microprocessors differs from a process optimized for fast turnaround gate arrays or high-volume RAMs. In a high-volume product, a great deal of effort is devoted to reducing the total number of process steps. For example, compensating blanket implants are often used to set the thresholds of the transistors to decrease the number of photolithographic masking steps. This approach couples the parameters for the NMOS and PMOS transistors, making parameter adjustments more difficult and requiring more development effort.

To produce high-performance microprocessors, Digital has developed many unique features for its CMOS technologies. Table 3 lists the new technology features that have been developed for each process generation to meet increasingly demanding performance requirements. We begin our discussion of the implementation of these features and the requirements for reliable circuit operation by addressing the issue of power dissipation in high-speed microprocessors.

# Power Supply Voltage

It is well known that CMOS power dissipation is dominated by  $C \times V_{dd}^2 \times f$ , where C is the switched capacitance,  $V_{dd}$  is the power supply voltage, and f is the clock frequency. A reduction in  $V_{dd}$  is an excellent way to counteract the increase in power due to

Table 3 Features Added by Generation for CMOS-1 to CMOS-4

|                      | CMOS-1              | CMOS-2                                 | CMOS-3                     | CMOS-4                     |

|----------------------|---------------------|----------------------------------------|----------------------------|----------------------------|

| Masks                | 12                  | 13                                     | 20                         | 21                         |

| Minimum<br>Dimension | 2.0 $\mu$ m         | 1.5 μm                                 | 1.0 μm                     | 0.75 $\mu$ m               |

| New                  |                     |                                        |                            |                            |

| Features             | 1X photolithography | Lightly doped drain<br>junction/spacer | 5X g-line photolithography | Local interconnect         |

|                      | n-well              |                                        |                            |                            |

|                      | Epitaxial layer     | Tungsten<br>silicide gate              | n, p-polysilicon           | Tungsten plug for M1C, M2C |

|                      |                     |                                        | Cobalt silicide            |                            |

|                      | Borophospho-        | Deep P+ ring                           |                            | Spin-on-glass              |

|                      | silicate glass      |                                        | TiN barrier                | etch-back                  |

|                      | planarization       | Photoresist                            |                            | planarization              |

|                      |                     | etch-back<br>planarization             | Al:1%Cu                    |                            |

|                      |                     |                                        | Metal 3                    |                            |

|                      |                     |                                        | Fuse                       |                            |

the higher frequencies and larger switched capacitance (which results from the increase in die size). When developing the CMOS-3 process, we chose to reduce the power supply voltage from the industry norm of 5 V to the Joint Electronic Device Engineering Council (JEDEC) 3.3 V standard.<sup>10,11</sup>

With the CMOS-4 process specified for 3.3-V power supply voltage, the NVAX and the Alpha 21064 microprocessors consume 16 watts (W) at 100 megahertz (MHz) and 27 W at 200 MHz, respectively. If the supply voltage were 5.0 V, the power would scale by  $(5 \text{ V})^2/(3.3 \text{ V})^2 = 2.3$ . This increase in power dissipation would have greatly increased the complexity and cost of the chip packages.

Significant changes to the NMOS and PMOS transistors were necessary to optimize the process for operation at 3.3 V. The most visible parameter change was a lowering of the target threshold voltages for the NMOS and PMOS transistors by about |0.4| V to 0.5 V and -0.5 V, respectively. To explain why this is necessary, we must consider the dependence of both the nodal transition time (which is a good measure of circuit performance) and the transistor currents on  $V_{dd}$ . The time required to transition a signal node between the power supply rails is proportional to the charge (Q) on the node and inversely proportional to the drain-to-source current  $(I_{ds})$  of the driving transistor. Since  $Q \propto V_{dd}$  and, to first order,  $I_{ds} \propto V_{dd}^2$ , the time required to transition a node is inversely proportional to  $V_{dd}$ . However, when second-order effects are considered, the 3.3-V technology is of about the same performance as the corresponding 5-V technology. The secondorder effects include the benefits from lowering the threshold voltages of the transistors in the 3.3-V process and the compromises that would have to be made to the transistors in the 5-V process to make them reliable.

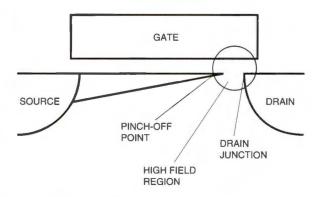

# Hot Carrier Degradation

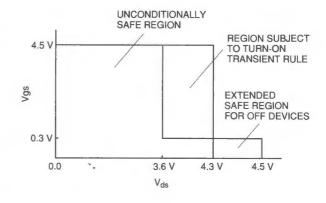

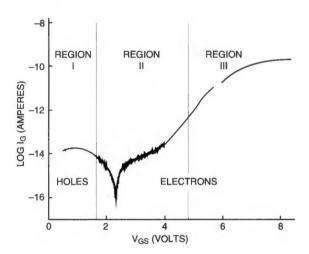

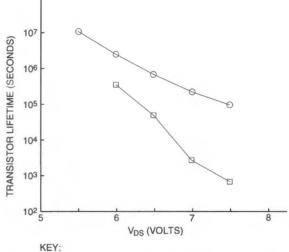

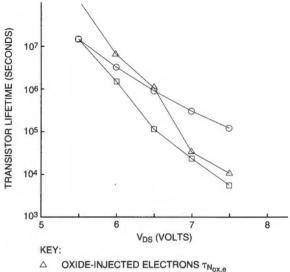

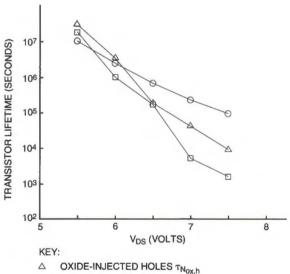

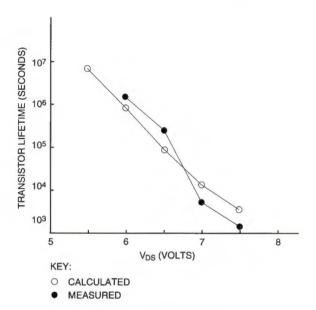

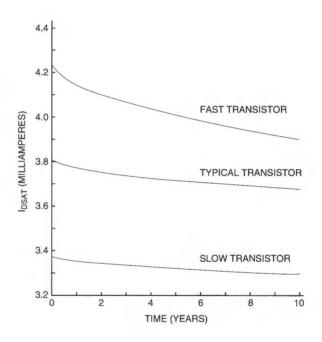

A CMOS transistor that is subjected to excessive voltages becomes damaged over time by hot carriers. Hot carriers are highly energetic current carriers that result from the high electric fields in the transistor. To date, the NMOS transistor has been more susceptible to hot carrier degradation than the PMOS transistor. Hot carrier damage gradually reduces the saturation current  $I_{DSAT}$  of the NMOS transistor as the damage increases over time. On chips with a nominal 3.3-V power supply, some transistors are subjected to source-drain voltage transients as high as 4.3 V. Table 4 gives details of the origins of these high voltage transients.

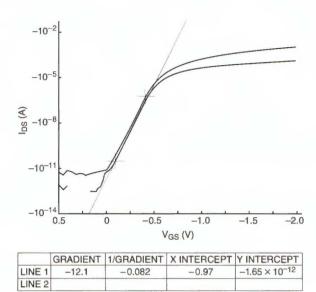

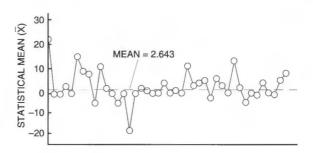

Hot carrier rules for the CMOS-4 process are illustrated in Figure 4, which shows the three legal regions of device operation on a plot of  $V_{gs}$  (gate-to-source voltage) versus  $V_{ds}$  (drain-to-source voltage). Devices may operate in any, or all, of three regions: (1) unconditionally safe region, (2) region subject to turn-on transient rule, and (3) extended safe region for "off" devices. Devices can spend up to

Figure 4 CMOS-4 Hot Carrier Rules

**Table 4 Origins of High Voltage Transients**

|                                                          | V <sub>ds</sub><br>(Volts) | Subtotal (Volts) | Comments                                                                                                             |

|----------------------------------------------------------|----------------------------|------------------|----------------------------------------------------------------------------------------------------------------------|

| Power supply                                             | 3.30                       | 3.30             | Nominal voltage                                                                                                      |

| Power supply tolerance                                   | 0.165                      | 3.465            | 5% tolerance, includes ripple                                                                                        |

| On-chip power supply ringing due to package inductance   | 0.175                      | 3.64             | From NVAX SPICE simulations. Half of peak-to-peak noise ( $V_{dd}$ _internal with respect to $V_{\rm ss}$ _internal) |

| Booting above V <sub>dd</sub> due to capacitive coupling | 0.66                       | 4.30             | Capacitive coupling to susceptible nodes is limited to <20% by designers                                             |

| Total                                                    | 4.30                       |                  |                                                                                                                      |

100 percent of the time in the safe region, no more than 5 percent in the region subject to turn-on transient rule, and no more than 10 percent in the "off" devices safety region.

A wide variety of NVAX circuits were simulated to determine what constraints should be placed upon circuit design style in order to ensure that the CMOS-4 hot carrier rules were not violated. A set of general circuit design constraints was developed, and a computer-aided design (CAD) tool was written to ensure that all the circuits on the NVAX chip observed these constraints. The hot carrier CAD checks were run prior to fabrication, and circuits that violated the constraints were redesigned.

# Electromigration Considerations

If the average current density ( $J_{average}$ ) through an aluminum conductor line is too high, the conductor line is susceptible to metal migration. This phenomenon occurs over time as the electron current forms voids at one site and deposits downstream. Eventually a short circuit or an open circuit develops, which results in a circuit failure. Chip designers guard against electromigration failure by ensuring that  $J_{average}$  for every conductor line on the chip is lower than the maximum allowed value.

For a conductor line that is switched every cycle, the relationship between average current density, microprocessor cycle time  $(T_{\rm cycle})$ ,  $V_{dd}$ , and cross-sectional area is given by  $J_{\rm average} = (C \times V_{dd})/(T_{\rm cycle} \times Cross-Sectional Area)$ .

It is interesting to note the changes to  $J_{average}$ for a conductor line as a chip is shrunk from one generation to the next. The node capacitance, C, decreases by slightly more than the scaling factor;  $V_{dd}$  remains constant;  $T_{cycle}$  reduces by the scaling factor since the chip can now run faster; and the cross-sectional area decreases by the scaling factor. Consequently,  $J_{average}$  increases by slightly less than the scaling factor as the width of the conductor line shrinks. If  $J_{average}$  now exceeds the maximum allowed value, the circuit must be redesigned. If there is enough space,  $J_{average}$  can be reduced by widening the conductor line so that the cross-sectional area is increased. From this brief analysis, it is clear that it becomes more difficult to observe the electromigration limits as the technology scales—even when the metal thickness is not scaled. As can be seen from the  $J_{average}$ equation, reducing V<sub>dd</sub> from 5.0 V in CMOS-2 to 3.3 V in CMOS-3 helped to counteract the effect of scaling on  $J_{\rm average}$ .

Scaling the interconnect and dealing with electromigration issues are some of the most formidable challenges that must be faced as feature sizes continue to decrease in the next decade.

#### Substrate Contact

As mentioned earlier, the substrate must be connected to the  $V_{ss}$  of the chip through a low-impedance path to prevent any rise in voltage. If the substrate voltage rise is severe, NMOS source/drain diodes will conduct, and if sufficient charge is injected, the chip may latch-up. Latch-up is a destructive mechanism involving the parasitic bipolar transistors formed by the CMOS process. The process, circuits, and  $V_{ss}$  substrate contact are designed to prevent latch-up from occurring.

The usual industry substrate connection method depends on a path through bond wires and the package to connect between internal  $V_{ss}$  and the substrate. To ensure a good substrate contact, Digital's CMOS technologies incorporate a deep P+ implant (DPI) around the edge of the die to connect the  $V_{ss}$  metal on the die surface to the low-resistance substrate. The implant creates a low-resistance path through the P-epitaxial layer in which the NMOS and PMOS transistors are formed.

The DPI is a low-inductance path when compared to the standard method that connects the substrate through the package. The additional area enclosed by the path through the bond wires and package implies greater inductance, which is undesirable for high-frequency signals. The DPI path between  $V_{ss}$  and substrate has low inductance because it is made directly on-chip.

# Technology-limited Gate Dielectric Thickness

As stated above, maximizing the current that a transistor can supply at a given  $V_{dd}$  is of uppermost importance for circuit performance. Scaling the transistor gate length, gate dielectric thickness, and threshold voltage improves the drive current. The transistor gate length is constrained by the minimum polysilicon line-width feature; the minimum threshold voltage is set by the leakage current allowed when the transistor is turned off. However, scaling does not establish a fixed relationship between feature size and gate dielectric thickness; scaling only determines the change from one generation to the next.

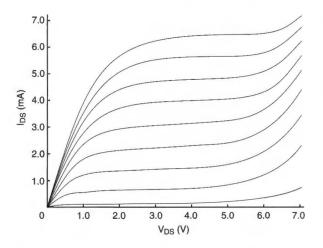

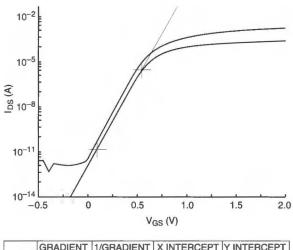

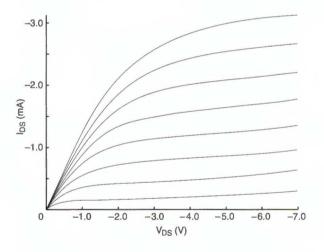

Figure 5 shows how the saturation currents for both NMOS and PMOS transistors in CMOS-4 depend on the gate dielectric thickness. The dielectric thickness range plotted spans applications from microprocessors to SRAMs. Both curves are only slightly sublinear; thinning the gate dielectric provides almost a one-to-one return in transistor saturation current. In high-performance microprocessor applications, reliability and manufacturability considerations determine the extent to which the gate dielectric thickness can be reduced. Digital's CMOS technologies have consistently used thinner gate dielectrics than industry norms.

Figure 5 Normalized Drive Current as a Function of Gate Dielectric Thickness for CMOS-4

#### Silicided Source/drain and Gate

The basic gate material for an MOS transistor is highly doped polysilicon. The sheet resistivity of this material in the CMOS-1 process was 40 ohms per square. For CMOS-2, the RC time constant delay associated with this sheet resistance would have created nonuniform turn-on of wide, fast-switching output transistors. A tungsten silicide layer was added to the polysilicon to form a polycide. The sandwich structure reduced the sheet resistance of the gate material to 3 ohms per square.

Changes to the transistor process for CMOS-3 technology, which were continued into CMOS-4,

required development of a new silicided gate process. The new process, known as salicide for selfaligned silicide, forms the silicide on the gate and on the source/drain regions after all the required transistor implants have been completed. This reduces the sheet resistance of the source/drain regions by more than an order of magnitude and allows them to be considered for use in local signal routing. The reduced sheet resistance, however, does little to improve the current drive of the transistor; for a typical CMOS-4 NMOS transistor, MINIMOS simulations show that the use of silicided source/drain regions improves the saturation current by only 0.6 percent.<sup>12</sup>

#### Precision Resistor

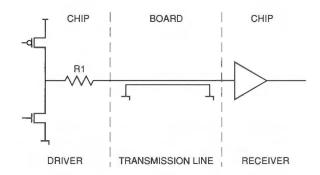

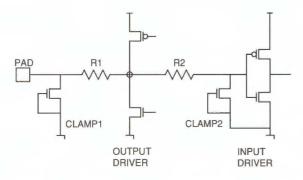

Although transistors are the dominant element in logic design, a resistor is sometimes needed, for example, to match the impedance of an output driver with the impedance of a board-level transmission line that it drives. MOS transistors make poor controlled impedance drivers because they change impedance as a function of drain voltage. One method of controlling the impedance of a driver is to use a diffusion resistor as the dominant element, as shown in Figure 6. The MOS transistors are sized such that their on-state resistance is much lower than that of the resistor. Therefore, if the transmission line impedance is 50 ohms, the resistor plus transistor impedance can be sized to match that value with little influence from the variations in transistor impedance.

Resistors are constructed from nonsilicided diffusion to meet tolerance requirements that would not be possible with a silicided version. Because a silicided resistor has lower sheet resistance, it is much longer and narrower than a nonsilicided

Figure 6 Precision Resistor Use in Impedance Matching

resistor of the same value. A narrow resistor is more susceptible to variations in field dielectric encroachment, which lowers the tolerance of the resistor. The tolerance is lowered further by process variation; it is more difficult to control the sheet resistance of the silicided diffusion than that of the nonsilicided diffusion.

The precision resistor is also an important element of our electrostatic discharge (ESD) protection strategy. Figure 7 shows a simple schematic of an I/O driver with the ESD protection components. Clamp 1 is the main path for shunting current during an ESD event. The position and construction of resistor (R) 1 and clamp 1 ensure that the clamp impedance is lower than that of a shunting path through R1 and the driver. R1 is also the impedance matching resistor for the output driver. R2 provides an additional level of protection for the gates of the input driver in conjunction with the smaller clamp 2 placed near the input driver. Both R1 and R2 are fabricated using the precision resistor mask layer.

Figure 7 Precision Resistor Use in Electrostatic Discharge Protection

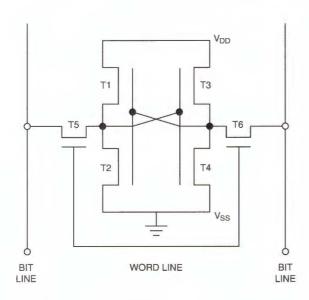

#### Local Interconnect in the SRAM

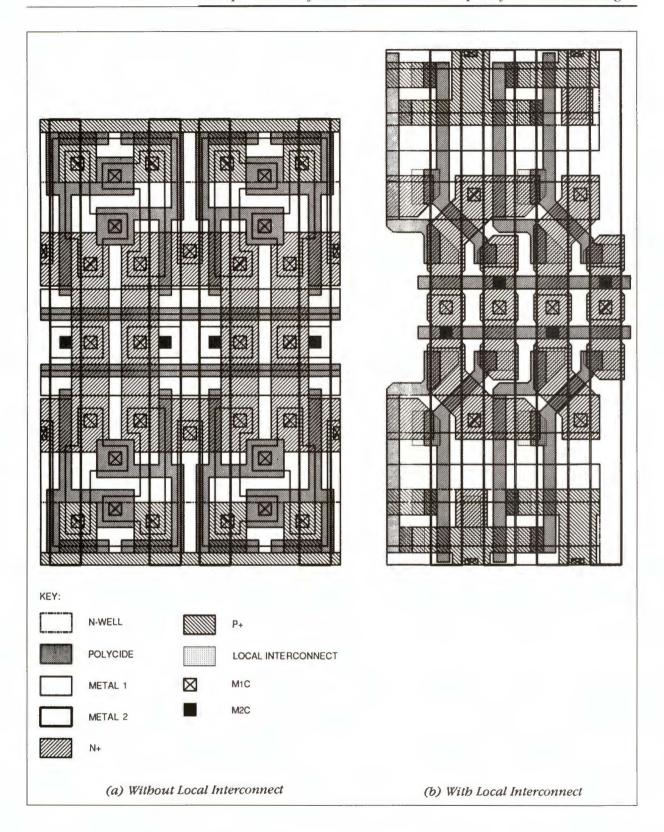

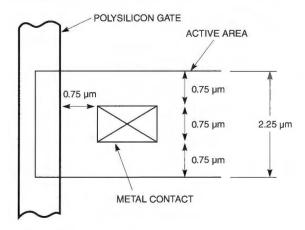

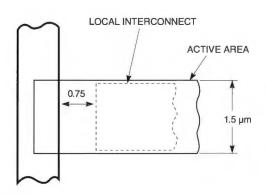

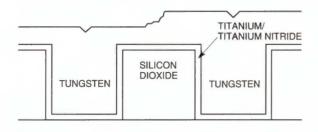

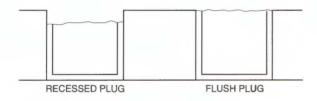

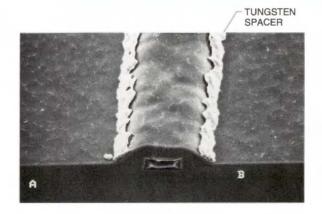

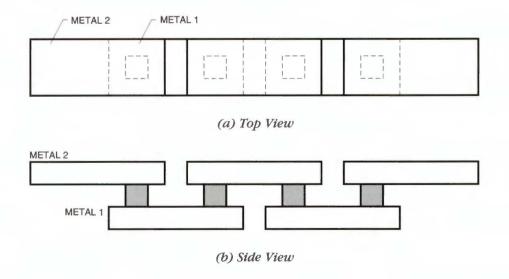

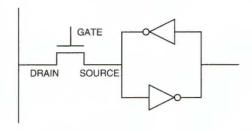

As stated earlier, one of the microarchitectural methods for increasing performance is to build as large a cache memory as possible on the die. Due to fabrication complexity, RAM-specific process enhancements are generally not implemented in a process tailored to microprocessors. However, the CMOS-4 technology does include one feature, called local interconnect, that significantly decreases the cell size. In the CMOS-4 implementation, local interconnect is a titanium-nitride (TiN) layer that provides direct contact between the polysilicon and diffusion layers. <sup>13</sup>

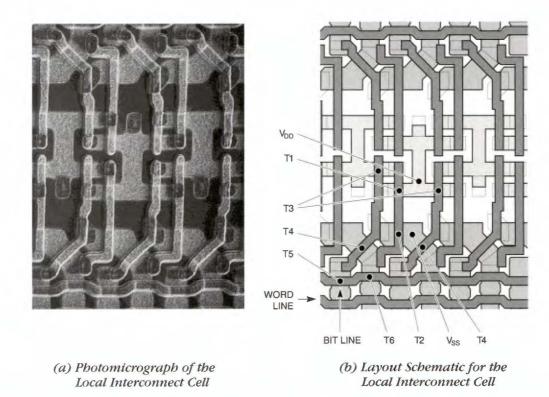

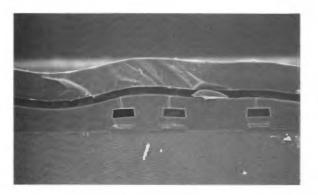

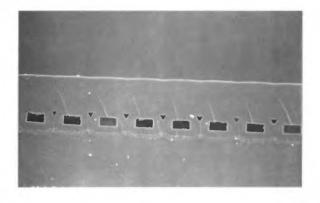

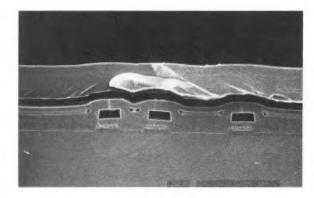

Figure 8 shows a comparison of layouts of memory cells with and without local interconnect. The

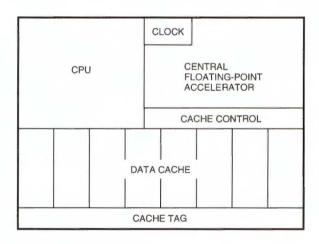

six-transistor static cell layouts show an array of four cells with the PMOS load transistors at the top and bottom of the arrays and the NMOS pass transistors, which provide access to the bit lines, in the center of the array. The cell without local interconnect is 120  $\mu$ m<sup>2</sup> in CMOS-4, compared to 98  $\mu$ m<sup>2</sup> for the cell with local interconnect. The 18 percent improvement in area is important, but the cell also has features that increase yield. There are only 2.5 contacts between the first level of aluminum interconnect (M1) and diffusion or polysilicon for the local interconnect cell, compared to 8 in the non-local interconnect cell. None of the M1 in the local interconnect cell is at minimum pitch (where pitch equals M1 width plus space), while all the M1 in the other cell is at minimum pitch. Finally, the M2 pitch is smaller in the local interconnect cell, but at 3.19  $\mu$ m, it is still greater than the minimum of 2.63  $\mu$ m allowed by the technology. All of these factors add up to a significantly more yieldable cell; this is important since 15 percent of the area and about two-thirds of the transistors on the Alpha 21064 chip are SRAM cells.

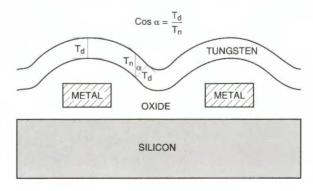

### Thick Metal 3 Interconnect

High-speed operation of the dense circuitry in large microprocessors results in a level of power dissipation not encountered in gate arrays or RAMs. The interconnect of a microprocessor has to carry tens of amperes of instantaneous current into and out of the chip in addition to routing signals. Furthermore, since high-performance microprocessor clock frequencies are of the order of hundreds of megahertz, the on-chip clocks must be distributed with very low RC time delay constants. These requirements lead to a number of differences between the interconnects used for microprocessors, gate arrays, and RAMs. RAMs at the 1- $\mu$ m feature size are usually designed with two levels of aluminum-based conductors (M1 and M2) that are very similar in thickness (approximately 1  $\mu$ m), minimum width, and spacing. Gate arrays generally add a third level of aluminum-based interconnect (M3) to improve signal routing and gate utilization in the array. This level has very similar characteristics to M1 and M2. Since the transistor density in a gate array is low and not all the gates are used in a design, the power dissipation is usually moderate by microprocessor standards.

The first two layers of interconnect on a highperformance microprocessor are very similar to the corresponding layers on an SRAM or gate array.

Figure 8 Six-transistor SRAM Cell Layout

However, because of the high power supply currents and low skew clock distribution required for high-speed operation, M3 in CMOS-3 and CMOS-4 processes is approximately 2.5 times thicker. To avoid an impact on yield, the pitch of M3 is chosen to be approximately three times larger than that for M2. To reduce capacitance to M1 and M2, the dielectric under M3 is thicker than that between M1 and M2.

### **Fuses**

As the number of memory cells increases on a microprocessor, the impact of those cells on the yield of the die increases. CMOS-3 and CMOS-4 technologies implement redundancy by a standard technique of laser-fusible links to remove bad cells and incorporate new ones into the array. Digital's process differs from others in the implementation of the fuses, however. Standard RAM processes use polysilicon fuses for their small size and ease of ablation. Because of the thickness of dielectric layers that would need to be etched to uncover the fuse, the CMOS-3 and CMOS-4 technologies could not use polysilicon fuses. Sufficient control of the dielectric etch rate and the selectivity of the dielectric etch to polysilicon cannot be achieved in a manufacturing environment for the thin polysilicon fuse layer to be left intact. Instead, the 80-nanometer (nm) film of TiN that forms the bottom layer of M3 is used. The upper layer of aluminum copper (AlCu) is selectively etched through a special mask to leave a 3- $\mu$ m wide strip of TiN that can be ablated by industry-standard lasers.14

Fusible links can be placed on a chip to form an identification register. A laser can then be used to program a unique code into this register. The contents of the identification register on the NVAX chip can be read by system software so that individual die can be uniquely identified not only during system manufacture, assembly, and test, but also in the field.

# Manufacturing Process Variations and Chip Design Strategy

As mentioned earlier, the performance of a CMOS process is a function of the current driving capability ( $I_{ds}$ ) of the PMOS and NMOS transistors, as well as the capacitances of the gates, sources, drains, and interconnect that the PMOS and NMOS transistors must charge and discharge. All of these parameters vary in manufacturing. In order to ensure that chips will function correctly and at the planned speed,

chip designers must account for these manufacturing process variations when the chips are being designed.

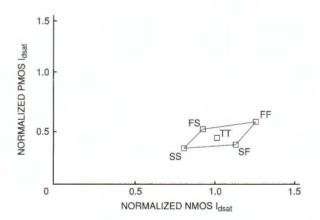

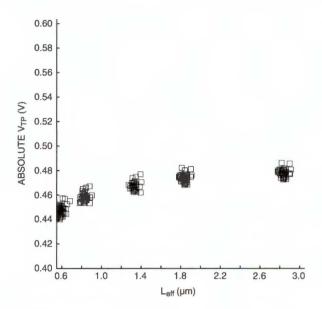

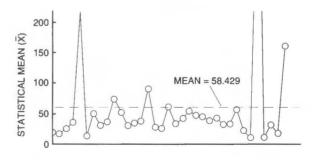

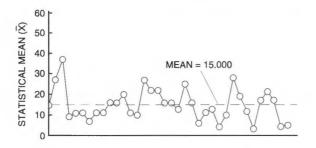

The lot-to-lot variation in characteristics for CMOS-4 transistors is significantly larger than for bipolar transistors. Figure 9 shows how the saturation current  $(I_{DSAT})$  varies in manufacturing for CMOS-4. The five points on the plot of PMOS  $I_{DSAT}$ versus NMOS  $I_{DSAT}$  represent the process extremes and are often referred to as the process corners. Each process corner has a two-letter label: FF, TT, SS, FS, and SF. The first letter of the pair is used to refer to the PMOS device: Findicates a fast (i.e., high current) device; S indicates a slow (i.e., low current) device; and T indicates a typical (i.e., manufacturing target current) device. The second letter of the pair refers to the NMOS device. Thus, the FF point in Figure 9 represents the fastest PMOS device paired with the fastest NMOS device; the SS point represents the slowest PMOS device paired with the slowest NMOS device; and the TT point represents a typical PMOS device paired with a typical NMOS device.

Figure 9 Comparison of Saturation Currents of NMOS I<sub>DSAT</sub> and PMOS I<sub>DSAT</sub> for CMOS-4 Process Corners

The FF SPICE<sup>15</sup> models are used to predict the speed of the fastest chips, the maximum power dissipation, the transient current demands on the power supply, the maximum voltage drops in the on-chip power and ground routing, the worst-case current density (checked to ensure that the electromigration limits are not violated) in power supply and signal lines, and the maximum rate at which the chip's signal pins will transition. Power supply current transients and signal-pin transition rates

have important implications for the electrical design of chip packages. Both place limits on how much inductance can be tolerated in the leads. The maximum power dissipation has obvious thermal implications for package and heat sink design.

The SS SPICE models are used to predict the speed at which the slowest chips will run. The TT models are used to check that the circuits on the chip will run at the desired speed when the manufacturing process is at the center of its range. The bulk of the circuit design work for the NVAX and Alpha 21064 chips was done using the TT models.

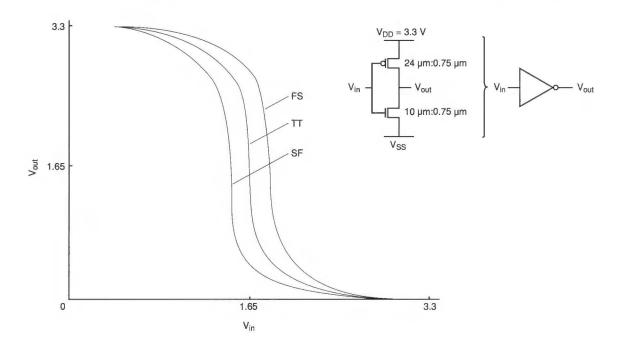

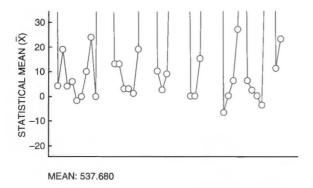

The FS and SF SPICE models are used to determine the noise margin for circuits (DC circuit analysis) rather than to predict the speeds at which circuits will run (AC analysis). The FS model has a semi-fast PMOS transistor paired with a semi-slow NMOS transistor; the SF model is just the opposite. The parameters that determine  $I_{DSAT}$  for PMOS and NMOS transistors are correlated. These correlations are taken into account in the FS and SF models. The correct operation of some CMOS circuits is particularly sensitive to the ratio of the PMOS to NMOS currents. By using the FS and SF models to simulate these circuits, designers can verify that the circuits will function correctly in spite of variations in the manufacturing process. A simple example is given in Figure 10, which shows how the switching point of a CMOS inverter changes from FS to TT to SF. Circuit designers use DC simulations like these to determine the safe bounds for the sizes of transistors in a variety of common circuit structures. These bounds are incorporated into the design methodology for the project, and CAD tools are used to search the circuit schematic database for structures that violate the methodology.

When creating schematics, circuit designers use technology-specific rules of thumb to estimate the interconnect capacitance on signal lines, etc. Layout for the schematics is then generated, exact capacitances are extracted from the layout using CAD tools, the capacitance estimates are replaced with the extracted values, and the circuits are resimulated to ensure that they still meet the specifications. The capacitance extraction tool can be rerun for a different process corner (dielectric thicknesses, etc.) by changing its parameter file.

Although not discussed here, environmental effects such as operating temperature and power supply variations must also be taken in account.

If CMOS chips are to be manufacturable, designers must account for process variations during the design phase by following procedures such as those just outlined. In order to get to market quickly, the NVAX microprocessor was being designed while the CMOS-4 process was being developed. Process

Figure 10 CMOS-4 Inverter Switching at Process Corners

simulators and test chips were used to generate the CMOS-4 worst-case and typical electrical models for transistors and interconnect during the early phase of process development. The accuracy of these models was critical to the successful and timely completion of the NVAX design: it was never necessary to redesign circuits due to process or model changes during the course of the project.

### Conclusion

Digital's CMOS processes have been developed specifically for high-performance microprocessors. Generation-to-generation improvements derived from scaling, increased die area, and new technology features have allowed increased performance every two years. The Alpha 21064 and NVAX chips, implemented in CMOS-4, are the highest performing reduced instruction set (RISC) and complex instruction set (CISC) microprocessors reported in the industry to date.

# References and Notes

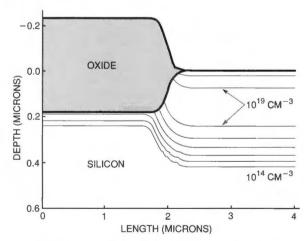

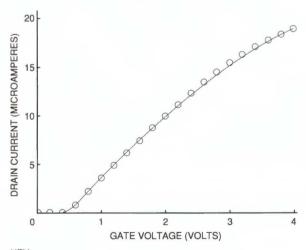

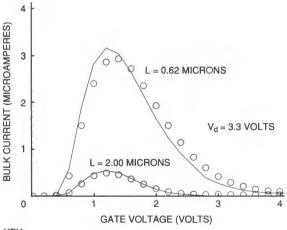

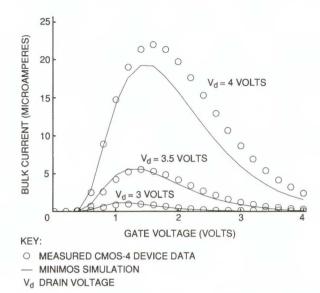

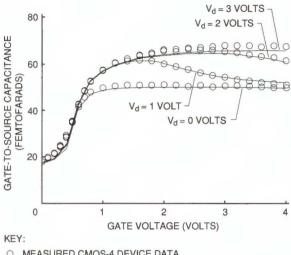

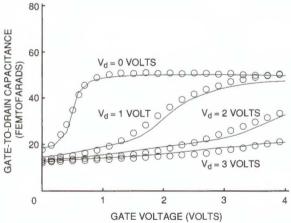

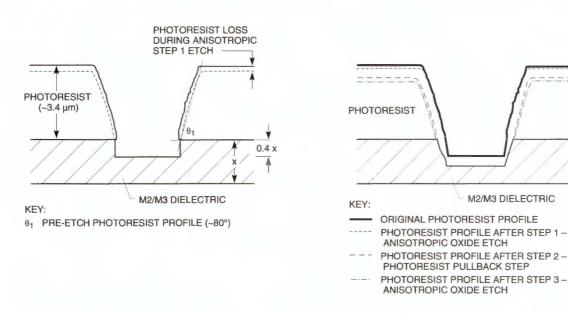

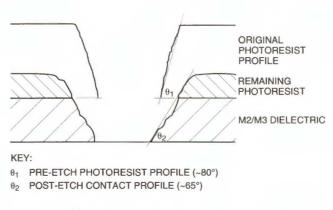

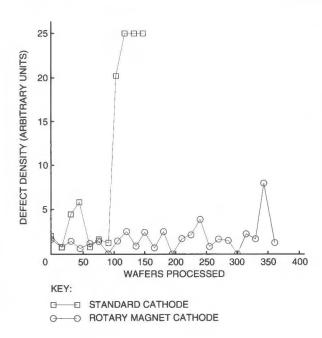

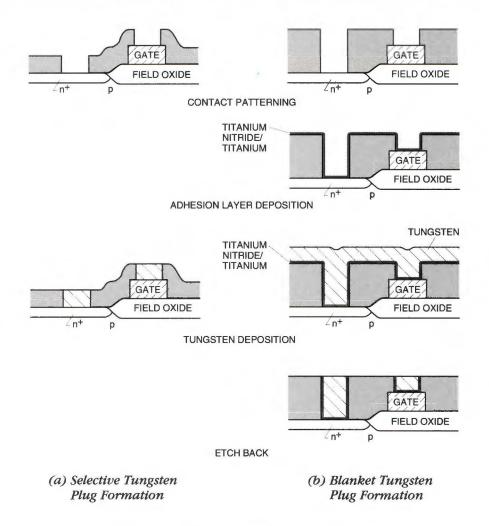

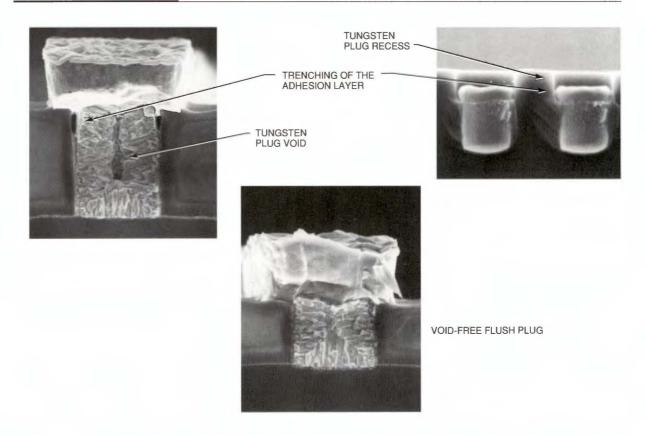

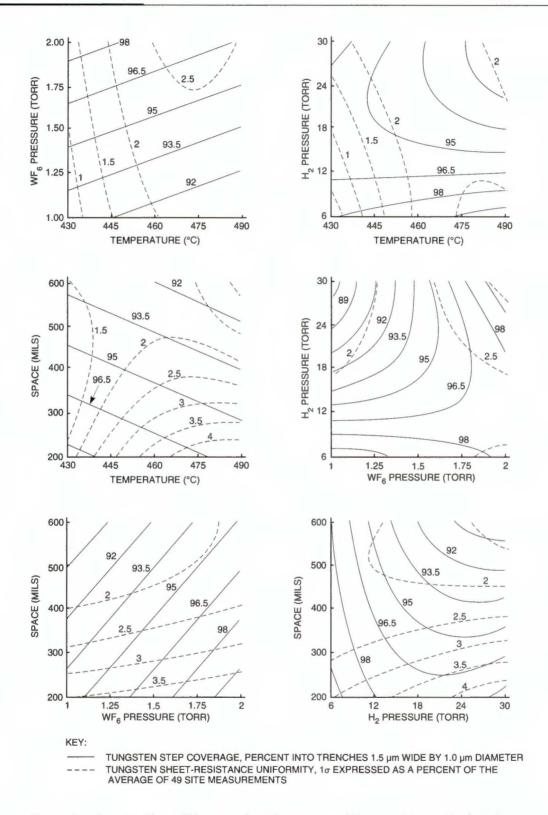

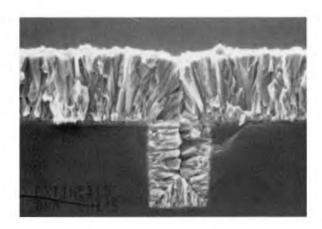

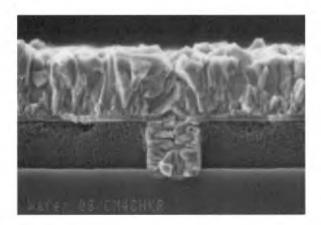

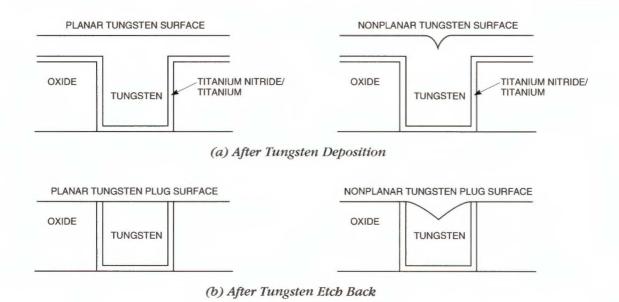

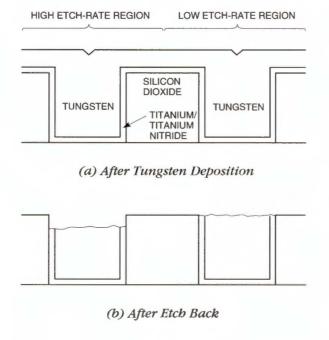

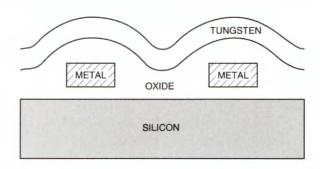

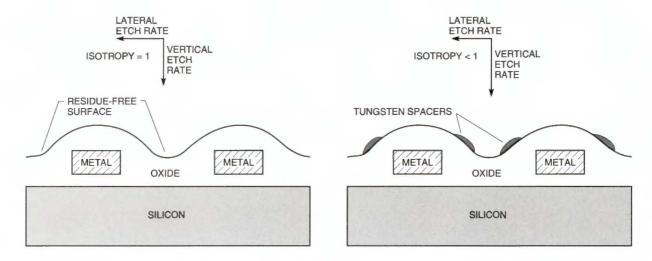

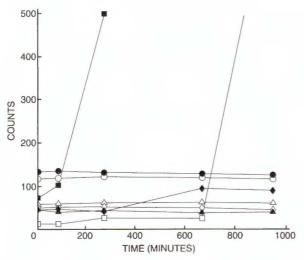

- 1. D. Dobberpuhl et al., "A 200MHz 64b Dual-Issue CMOS Microprocessor," *IEEE International Solid-State Circuits Conference Digest* of Technical Papers (February 1992):106–107.